基于香橙派鲲鹏Pro开发板的开源EDA软件Digiblock的入门实践

发表于 2025/06/11

0

作者|楼佳明

1.案例介绍

1.1 Digiblock介绍

Digiblock是一款集成开源工具链的图形化EDA软件,无需verilogHDL编程,即可在仿真环境中运用门电路以及图形化模块,“搭积木”式的构建数字逻辑电路,甚至复杂的CPU系统,并且通过行为级的仿真直观的展示数字电路运行状态,简单易用,功能完整,性能优越。同时,Digiblock可以将图形化仿真工程直接转化VHDL及verilogHDL文件,并且配套自动例化的testbench模板,还可以支持图形化模块与verilog代码混合仿真。进一步,Digiblock通过开源的iVerilog引擎+GTKwave波形查看器,可以支持Verilog的时序仿真与验证。Digiblock可以贯穿计算机组成原理、体系结构、汇编语言及EDA设计等计算机专业基础课程的理论学习与实验,为计算机、电子信息及自动化等专业的学生提供巨大的帮助。

本案例讲述Digiblock软件的基本使用方法,介绍数字电路逻辑门元件,以及使用Digiblock的组合逻辑设计工具实现逻辑表达式或真值表,让开发者顺利入门Digiblock,为后续使用Digiblock进行ARMv8 架构CPU(香橙派鲲鹏 Pro开发板上所用CPU)设计打下坚实的基础。

1.2 关于本案例环境

本案例基于香橙派鲲鹏 Pro开发板上的鲲鹏处理器和openEuler操作系统。

openEuler是一款支持多样性设备、覆盖全场景应用、具有完整开发工具链的面向数字基础设施的开源Linux操作系统,支持x64和arm64等多种处理器架构,更是鲲鹏处理器天然的基础软件设施。

有关openEuler的详细介绍和资源可以参考如下网址:

有关鲲鹏硬件更多的资料可以参考鲲鹏论坛。

1.3 案例设备介绍

关键配置如下图所示:

资源 | 规格 |

香橙派鲲鹏pro开发板1台、HDMI线1根 | 开发板:4核鲲鹏CPU,16G内存 |

个人pc | 需要可以和开发板正常连接 |

键盘、鼠标、显示器 | 一套 |

用户及密码 | root用户对应密码(openEuler) |

2.案例环境搭建

2.1 连接并登录到香橙派鲲鹏pro开发板

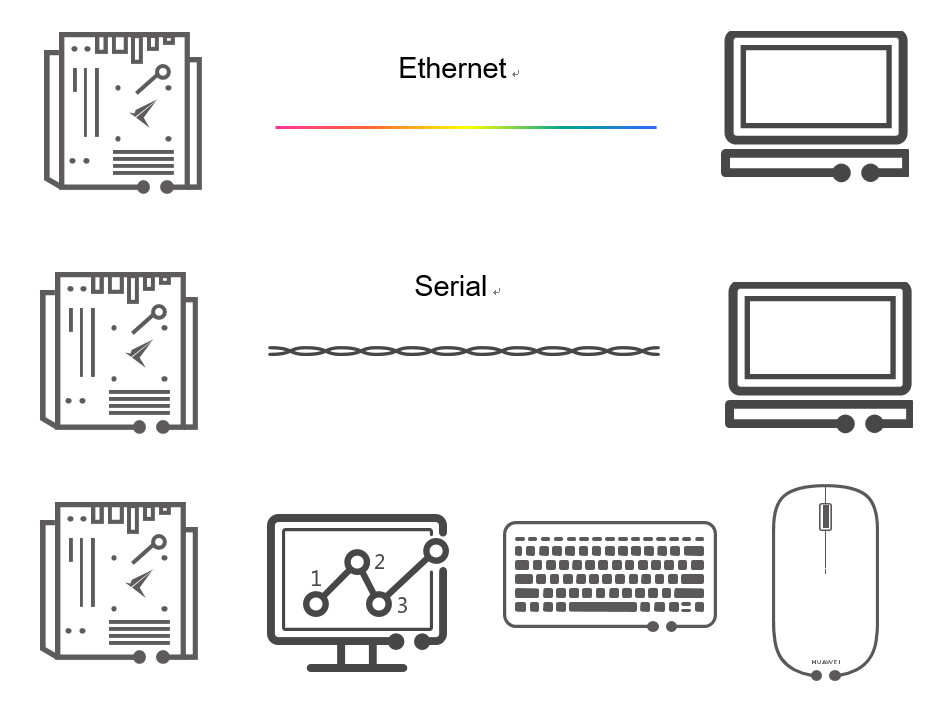

2.1.1 实验设备的连接

由于Digiblock的软件使用必须需要用到图形化的操作系统,本案例通过:“开发板+显示器+键盘+鼠标相连”的方式进行连接。

2.1.2 硬件连接

步骤 1 通过独立主机连接开发板

香橙派鲲鹏 Pro开发板上安装的是图形化桌面的openEuler操作系统,所以可以通过开发板上的HDMI接口连接到显示器上。本方式硬件连接如下所示:

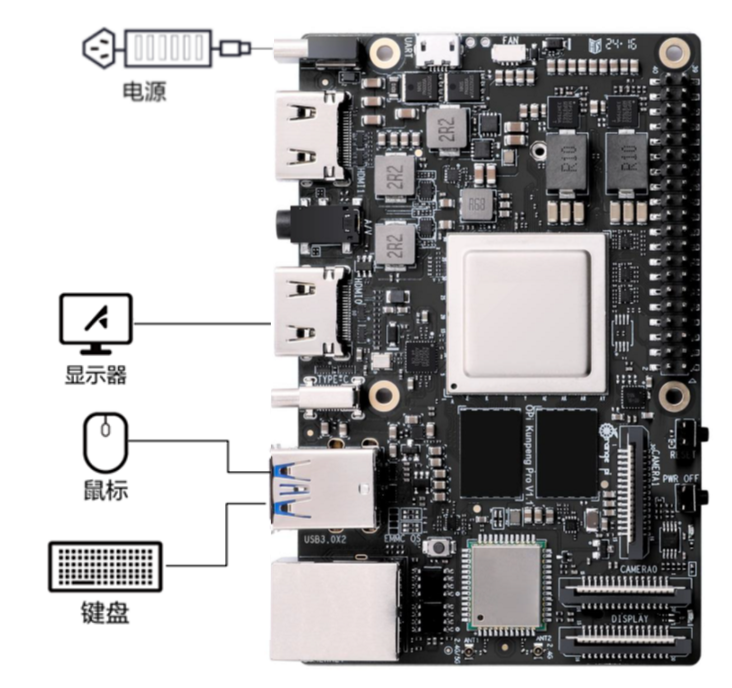

步骤 2 开发板连接显示器、鼠标、键盘

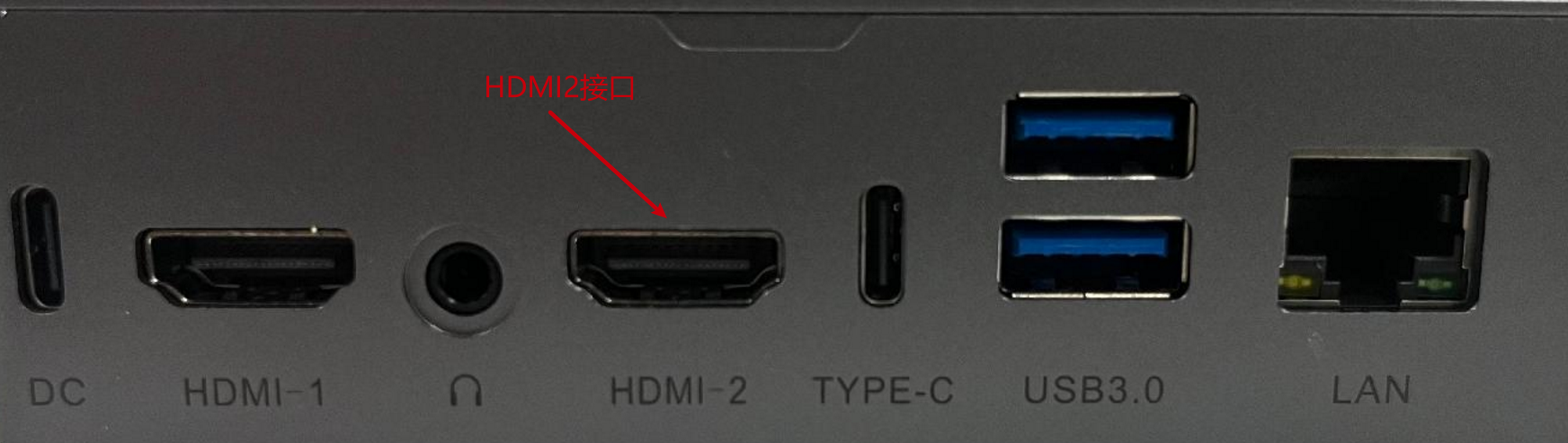

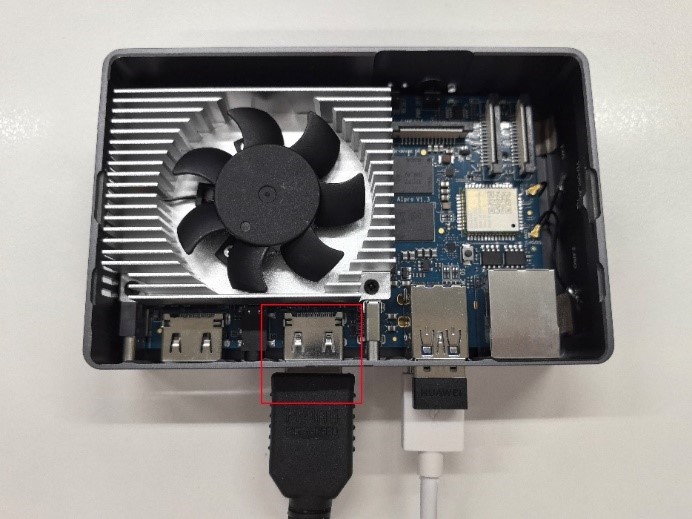

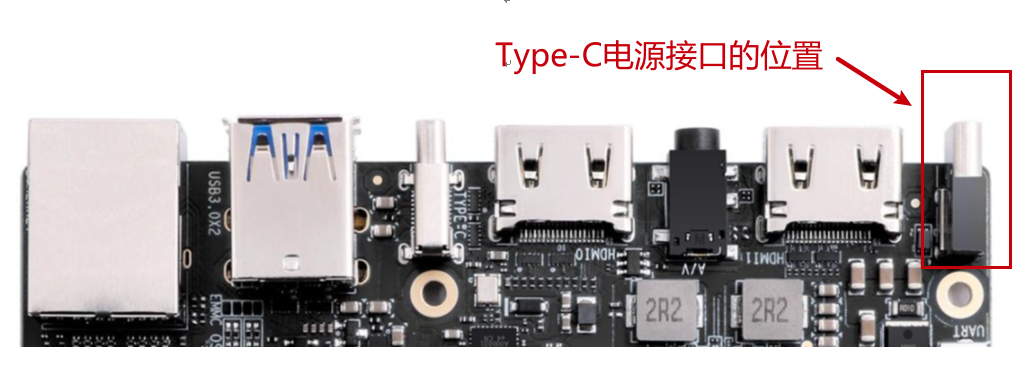

将显示器连接到开发板的HDMI2接口,如下图:

*注意:开发板有两个HDMI接口,目前只有HDMI2支持显示Linux系统的桌面,HDMI1显示Linux系统桌面的功能还需等软件更新

通过开发板USB接口连接鼠标、键盘:

步骤 3 开发板连接电源

连接20V PD-65W的Type C接口的电源,电源接口的位置如下图所示:

靠近关机按键的绿灯为电源指示灯,绿灯亮起代表开发板上电成功;MIPI LCD和CAMERA0 之间的绿灯为SATA硬盘的指示灯,绿灯亮起说明Linux内核启动成功:

2.1.3 登录到图形化桌面的openEuler操作系统中

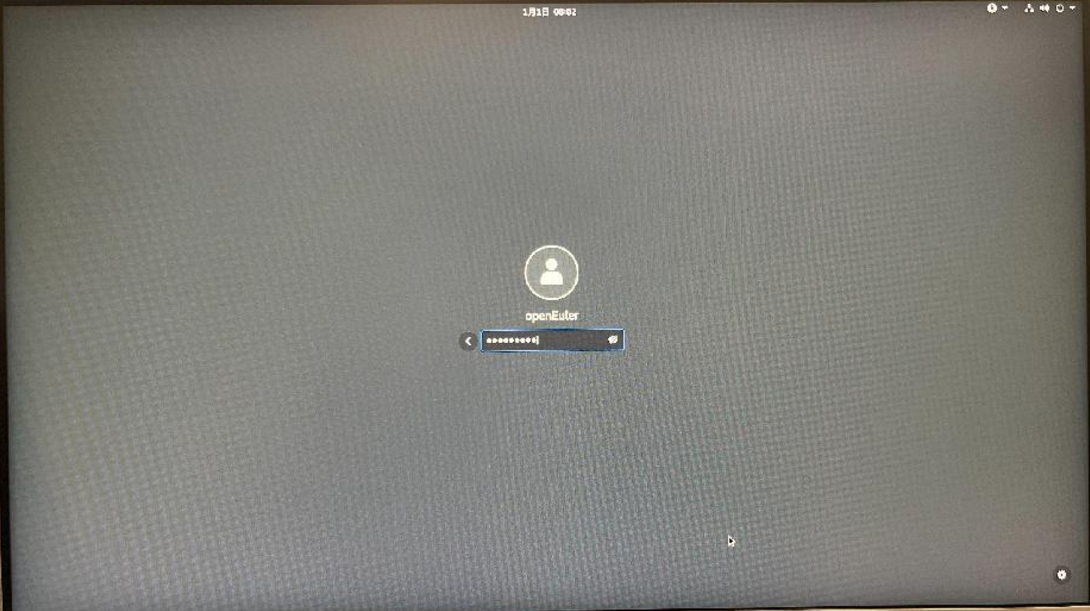

硬件正确连接后,可以看到显示器中出现了登录界面,默认用户为openEuler,输入默认密码openEuler,然后输入回车键。

进入到图形化桌面的openEuler操作系统中,界面如下图所示。

2.2 开发板网络连接

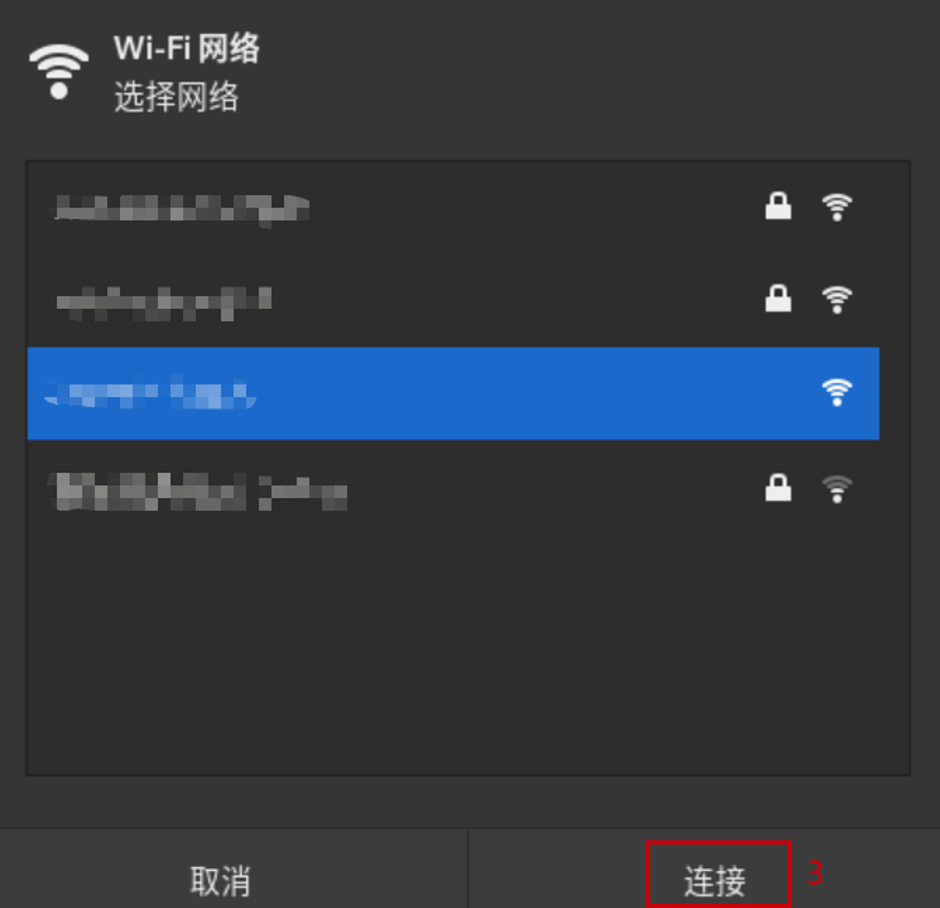

先点击桌面右上角的倒三角型▼图标,然后点击Wi-Fi未连接。

接着选择要连接的网络名称,点击连接。

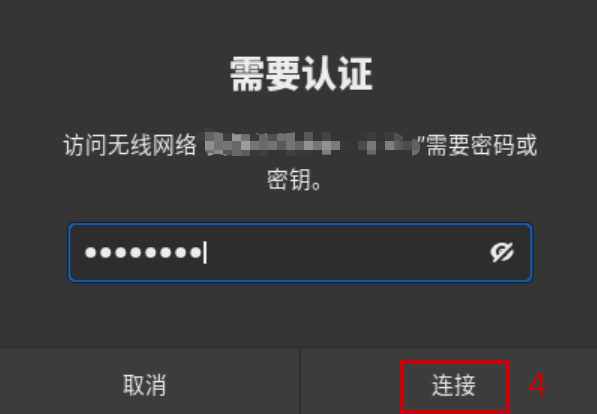

最后输入密码进行连接。

3.实验操作指导

3.1 运行Digiblock

Digiblock是基于Java虚拟机运行的软件,使用前必须先安装Java虚拟机JDK1.8及以上的版本(开发板自带的环境为java11.0.24,所以无需在安装)。若需要支持Verilog代码的时序级仿真验证,则还需要配置开源仿真器iVerilog及其配套的GTKwave软件(香橙派鲲鹏 Pro开发板已经内置iverilog和gtkwave)。Digiblock软件本身不需要安装,从gitee上下载即可。其目录(如下图所示)可以放置在硬盘任何地方, 运行Digiblock.jar即可运行Digiblock,打开其界面。具体操作如下。

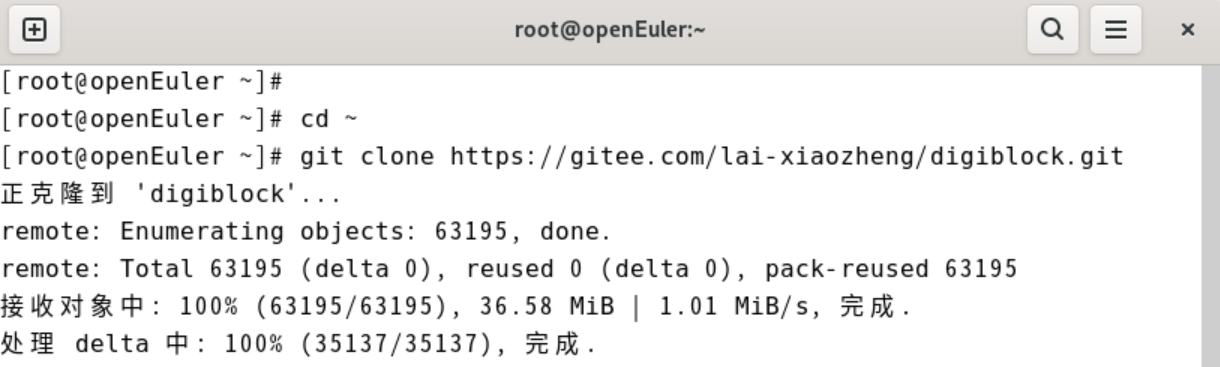

步骤 1 下载Digiblock

登录操作系统后,先点击左上角的活动,然后点击终端。

在终端中输入以下命令,通过git命令从码云网站上下载Digiblock。

cd ~

git clone https://gitee.com/lai-xiaozheng/digiblock.git

步骤 2 找到下载目录

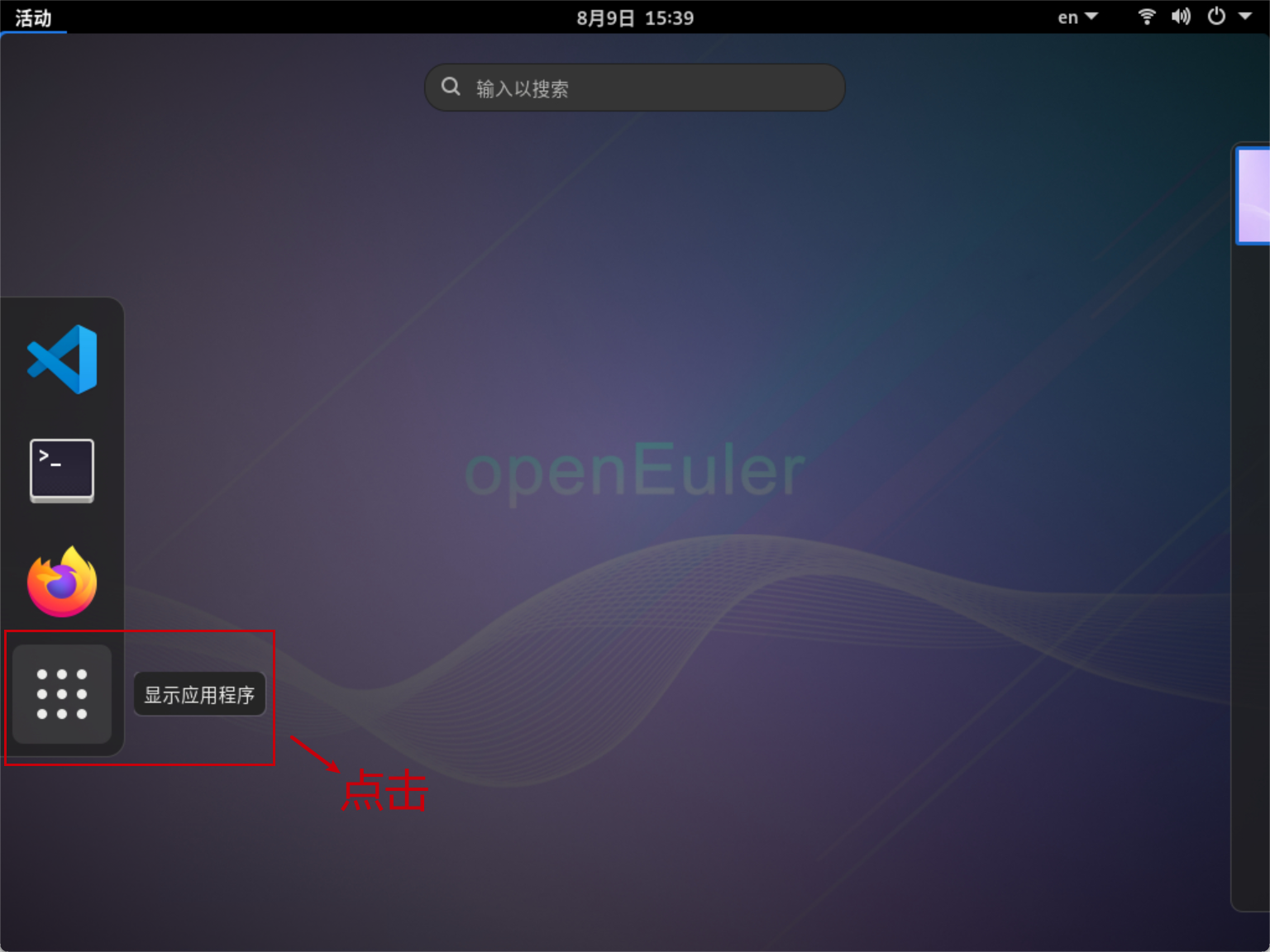

登录图形化界面后,点击左上角的活动。

点击显示应用程序的图标。

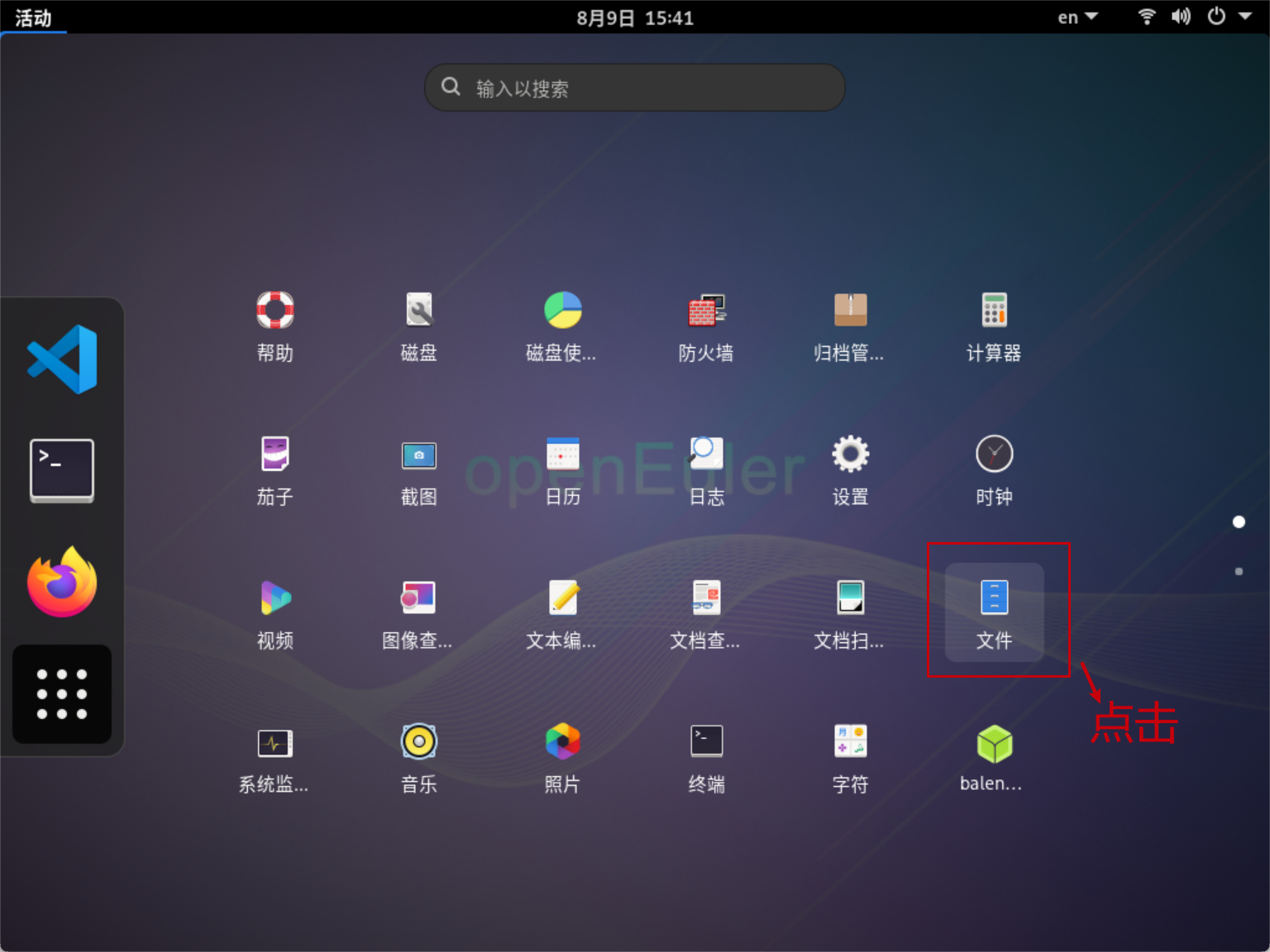

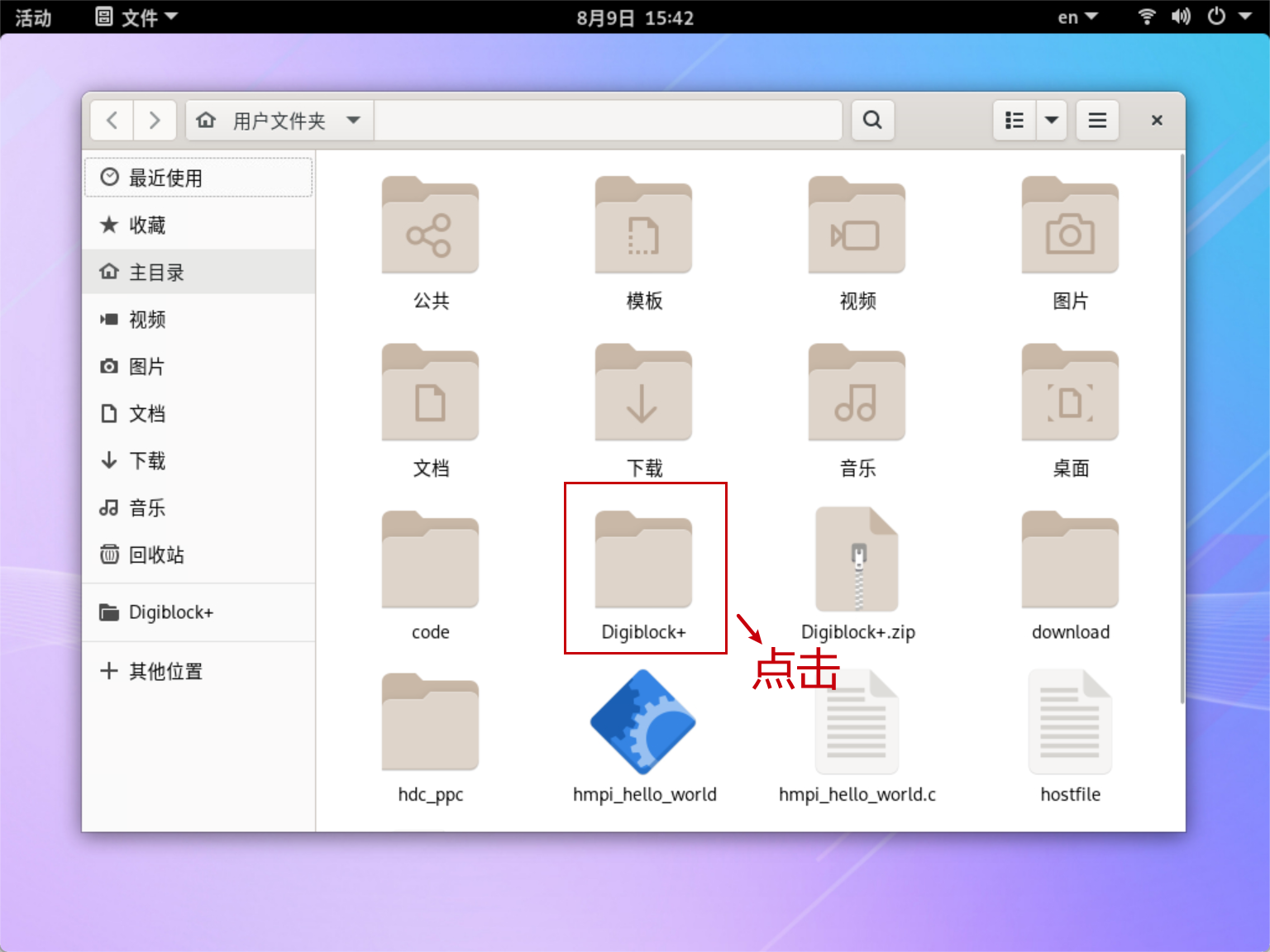

点击文件图标。

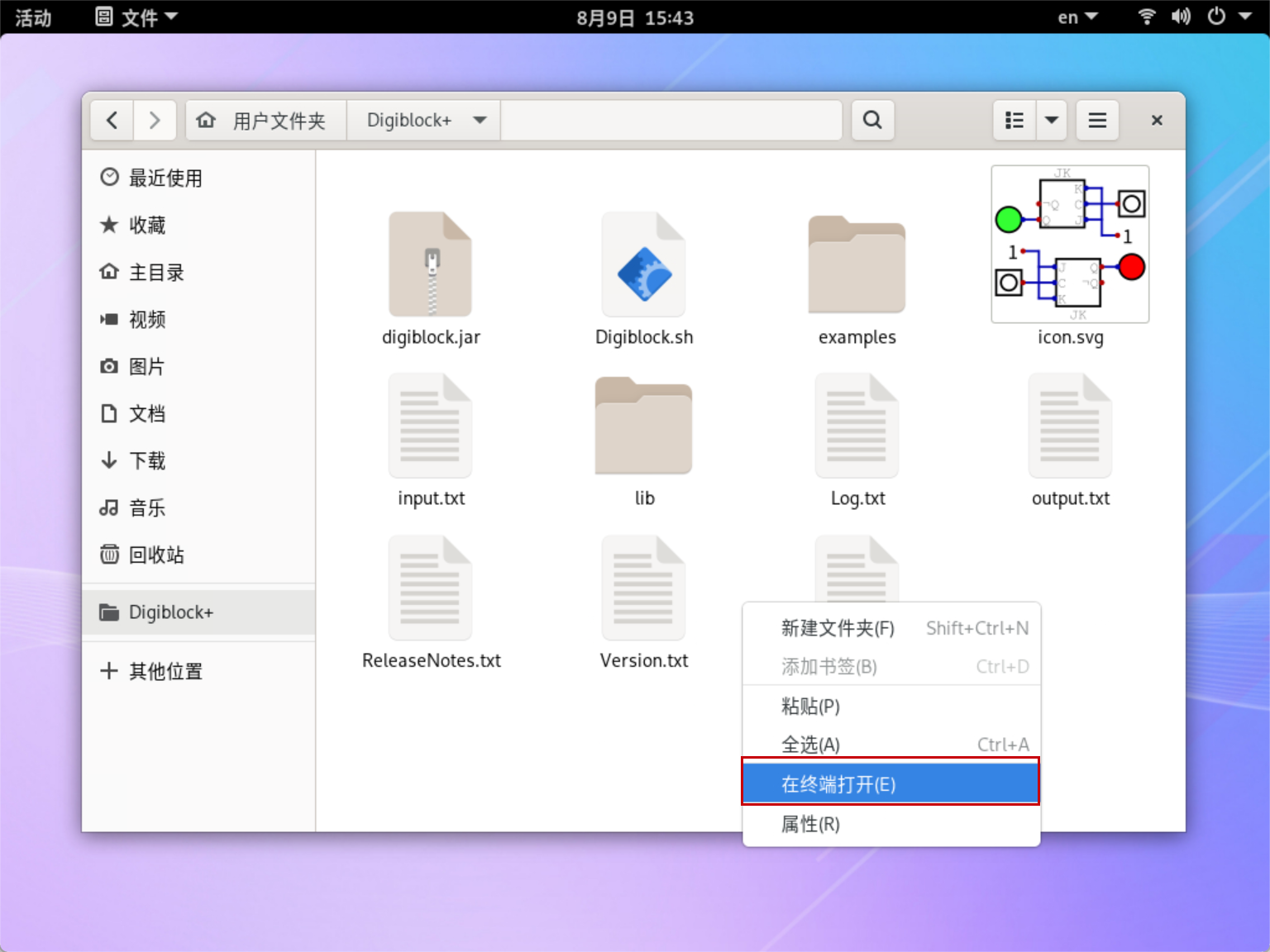

点击Dibiblock+文件夹。

步骤 3 运行Digiblock.jar文件

鼠标右键点击空白处,然后点击在终端打开。

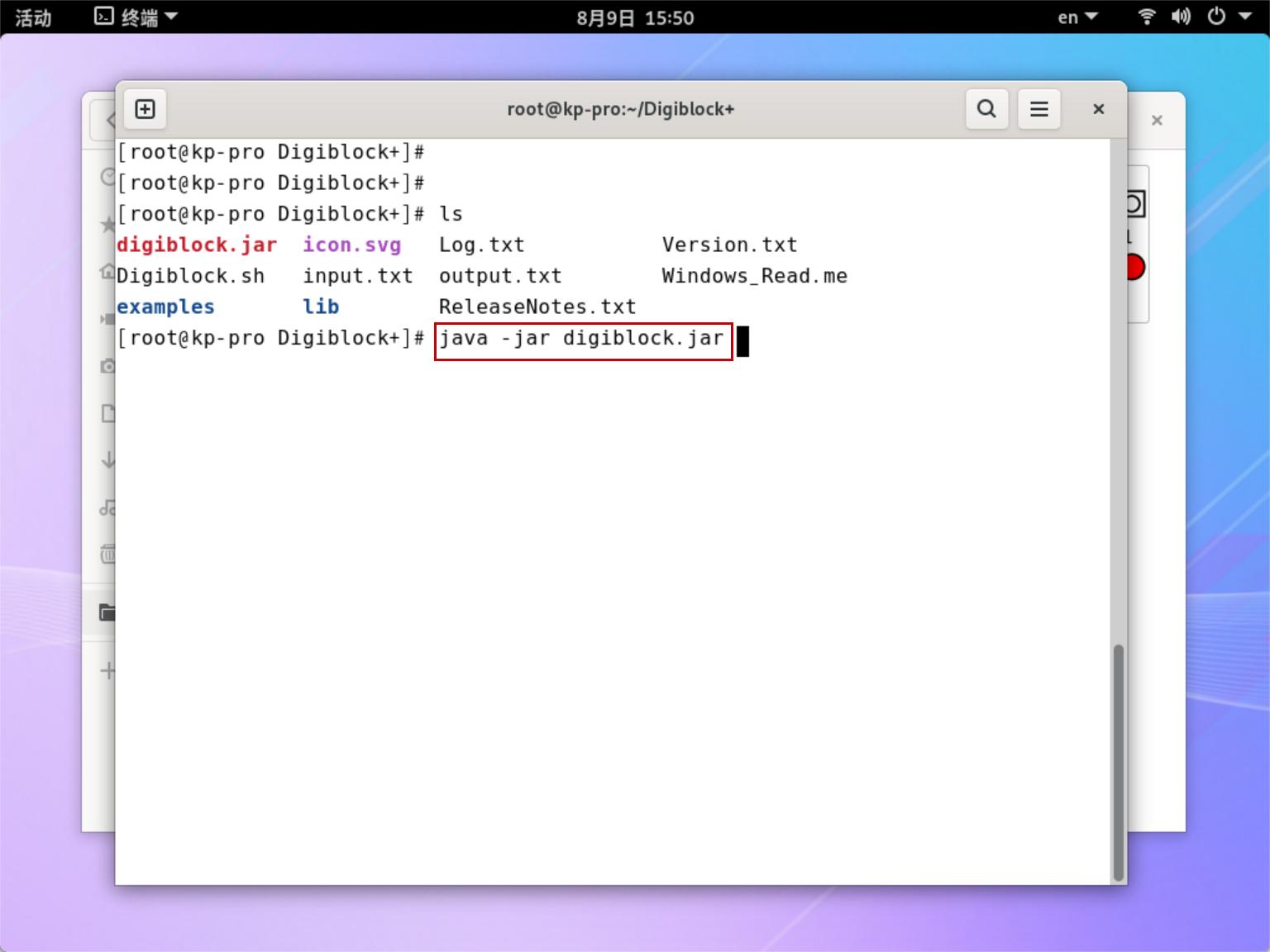

在终端输入 java -jar digiblock.jar命令。

java -jar digiblock.jar

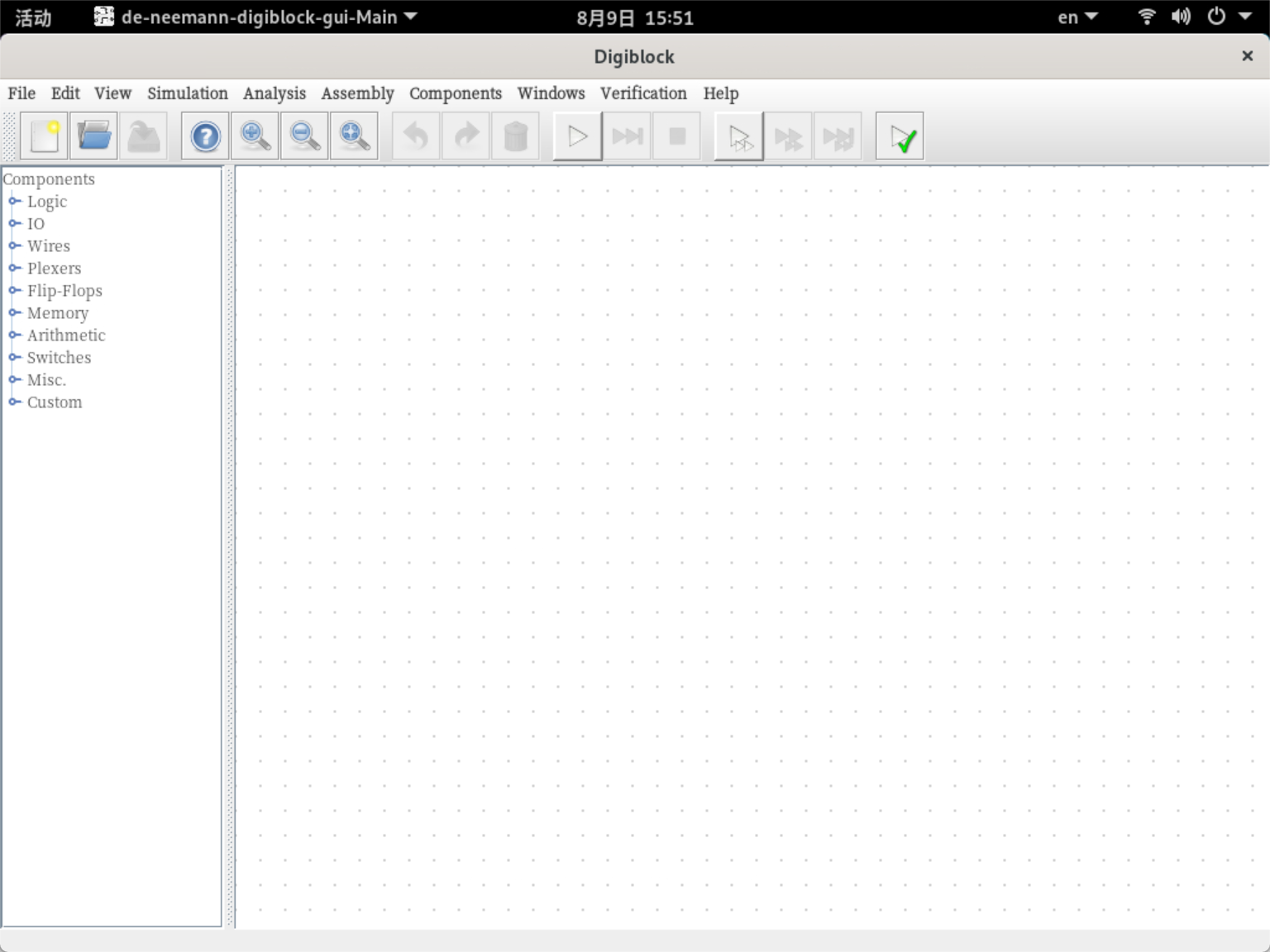

成功打开Digiblock软件。显示结果如下:

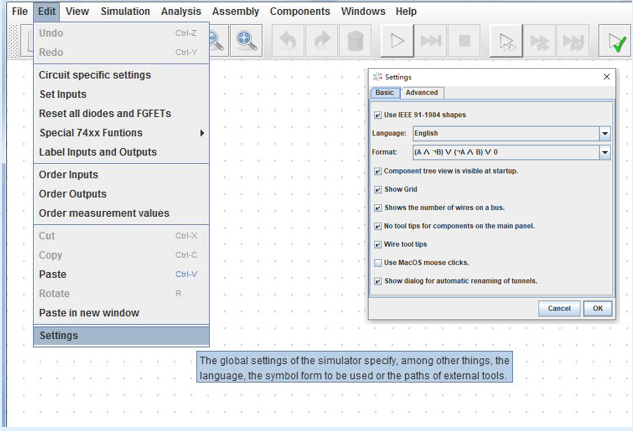

步骤 4 配置Digiblock

Digiblock界面首次打开后需初始化设置,选择”Edit->settings”路径打开Settings界面,可以选择配置语言,逻辑表达格式,(是/否)显示元件树,(是/否)显示网格等等选项,下图中的配置是默认配置(语言建议选择English),设置完成后关闭Digiblock界面,重新启动软件后,选项才会生效。

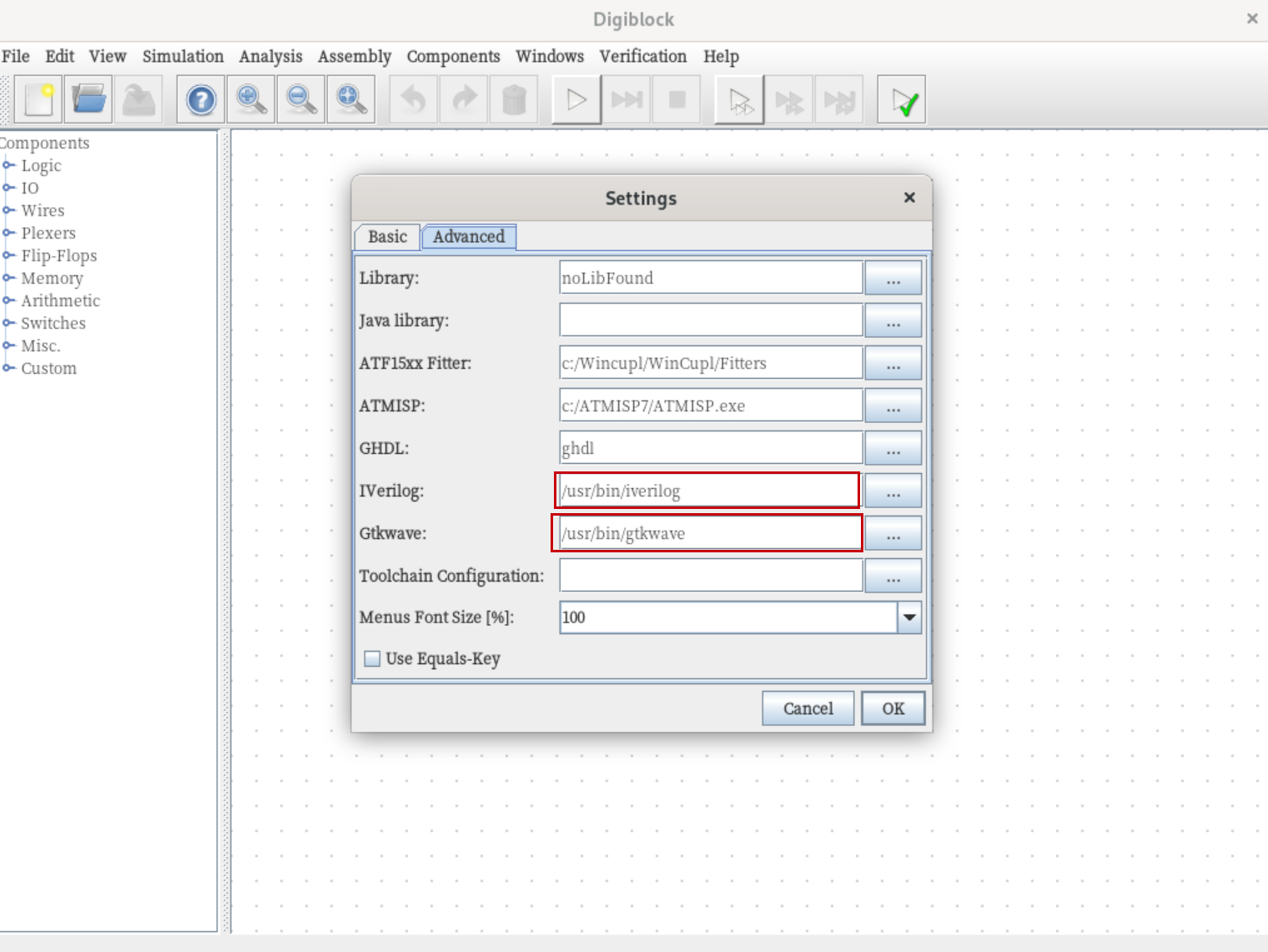

如左下图所示,Digiblock工具链中的iVerilog开源仿真器提供对Verilog代码的仿真功能,GTKwave工具则提供仿真结果的波形图形式。这两个软件需要单独安装,而且要指定安装路径。

如右下图所示,选择”Edit->settings”路径打开Settings界面,在进阶配置Advanced框内可以指定iVeilog和Gtkwave工具的执行文件所在路径。如果用户选择输出VHDL文件,则需要安装GHDL开源仿真器,并且在页面上指定GHDL的执行文件所在路径。

3.2 Digiblock基本使用

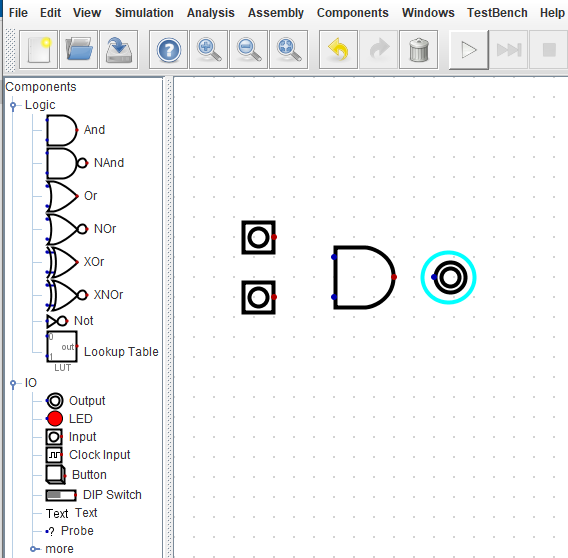

如左下图所示,重新打开的Digiblock界面可以看到界面左侧Component树状图,点击树状图Components下面的节点“0-”可以展开,点击第一个节点“0-Logic”前面的“0-”,可以看到“Logic”节点下有And(与门)、NAnd(与非门)、Or(或门)、NOr(或非门)、XOr(异或门)、NXOr(同或门)、Not(反相器)门电路以及Lookup Table(查找表LUT);点击第二个节点”0-IO”可以选择输入端口Input,输出端口Output,按键Button,灯LED,文本框Text、时钟信号源Clock Input、拨码开工DIP Switch、探针Probe等等电路。鼠标在类似上述的元件图标上左键点击,则右边的空白界面内会出现一个悬浮的被蓝色框圈住的对应元件,且跟着鼠标移动。界面内任何位置上左键点击,即可把该元件放在点击的位置上。左下图中放入了一个And与门电路,一个输出端口Output以及两个输入端口Input。

如右下图所示:在已经安放好的元件上鼠标左键点击,可以使该元件回到被蓝色框圈住的悬浮状态,跟随鼠标移动,再在新的位置上左键点击,就可以把元件固定在新的位置上。

如右下图所示,若要移动一组(若干个)元件,可以鼠标左键在界面空白处点击,按住不放沿着对角线拖动,再释放鼠标左键,则对角线的两点形成一个虚线框,把需要移动的若干个元件圈在虚线框内。此时,虚线框内的所有元件都会变成被蓝色框圈住的悬浮状态。在虚线框内鼠标左键按住不放,拖动鼠标即可把整个虚线框移动,到指定位置后鼠标左键释放,则所有元件将安置在新的位置上,且彼此的距离和连线不变。

无论移动一个或一组元件(虚线框),若在移动过程中鼠标右键点击,则撤销整个移动操作,被移动的所有元件回归原位。

若要删除某个元件或一组元件,可以选中后(蓝色框住某个元件或虚线框住一组元件),直接按Del键。

若已经被蓝色框圈住的元件需要释放,则鼠标左键在界面空白的任意位置点击,即把整个界面中所有悬浮状态的元件恢复正常(取消蓝色框和虚线框)。

仔细观察右上图,会发现输入端口元件INPUT的图标上有一个红色连接点,而输出端口元件OUPTPUT的图标上则是一个蓝色连接点!在Digiblock中,元件之间通过连线实现信号互通,红色连接点代表元件输出端,蓝色连接点代表元件输入端。因为输入端口Input只能输出信号给其他元件,所以只有一个红色连接点(输出);同样,输出端口Output只能从其他元件输入信号,所以只有一个蓝色连接点(输入)。而与门And就有左边两个蓝色连接点(代表与门的两个输入端)和右边一个红色连接点(代表与门的输出端)。

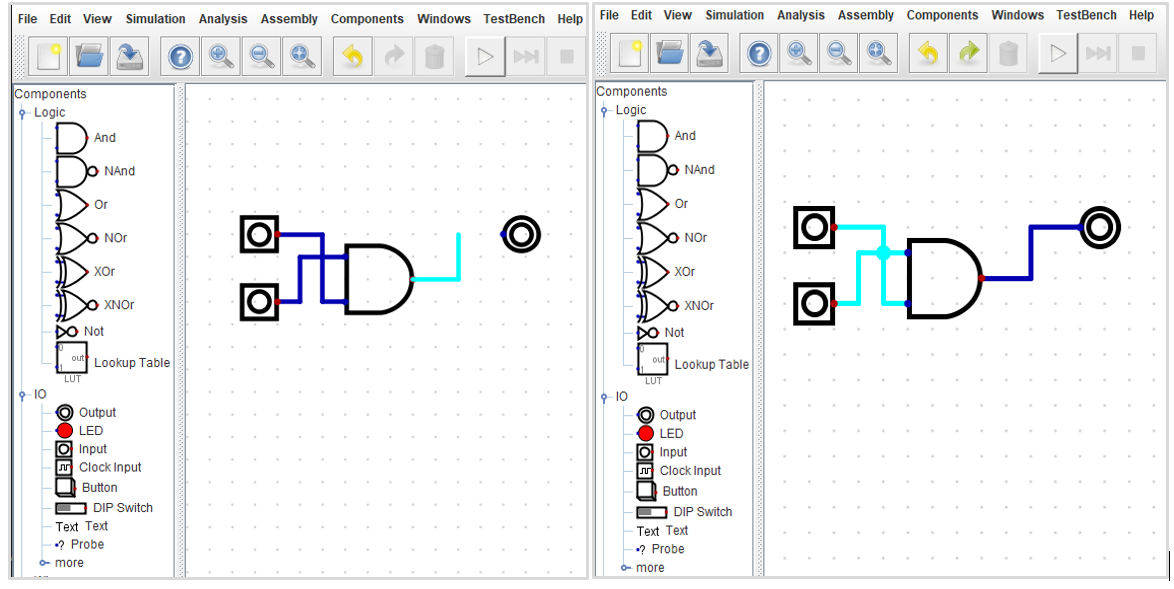

如左下图所示,鼠标在元件的连接点左键点击,可以开始绘制连线,连线随着鼠标移动不断延长,若鼠标改变方向还会自动形成弯折线(仅能形成一个弯折)。

在上述鼠标移动过程中,连线是蓝色的,表示连线仍在绘制中,还没确定下来。在移动的过程中,鼠标若再次左键点击则把当前的连线完成了(从蓝色变回正常)。此时,若连线完成的位置不是元件的端点,则从该位置产生新的未完成的连线跟随鼠标移动。若不需要继续连线,右键点击撤销操作(所有蓝色连线都消失)。

鼠标左键点击完成连线时,若该位置是某个元件的连接点(端口),则建立了两个元件之间的电气连接。若该位置不在元件的连接点上,则连接线悬空。在Digiblock中,连线必须是从一个元件的输出端到另一个元件的输入端,不允许两个输出端或输入端之间互连。也不允许连线悬空,否则出错。若连接线悬空,必须在该点继续左键点击,绘制连接线,到另一个元件的端口为止。

若上述移动过程中,鼠标经过其他连线时(此时移动的连线与该连线交叉)停下左键点击,则在两条连线交叉处形成节点,表示两条连线有电气连接;若没有左键点击,则没有形成节点,即交叉的两条连线没有电气连接。如左下图中两个输入端口与And元件的连线交叉但无节点,即两个输入端各自独立,没有电气连接。而右下图中则两个输入端口与And元件的连线交叉了,说明两条连线之间有电气连接(两个输入端之间互联,出错)。

此外,鼠标放在任意一条连线上,则所有与该连线有电气连接的连线和该连线自身一起变蓝色,如右下图所示。在复杂电路连线时,该功能可以方便识别元件之间的连接关系。鼠标也可以通过画虚线框的形式选中某段连线(使其变蓝色),只要该连线的部分在虚线框内,即可被选中。选中后的连线可以按下Del键删除,也可以随着鼠标拖动(鼠标在虚线框内左键按住拖动),但是由于选中的连线移动时其相连的元件(没有被虚线框住)不动,所以仅拖动连线时容易使连线弯曲变形。一般建议是连线及其所连接的元件一起移动,保证连线走线的笔直。

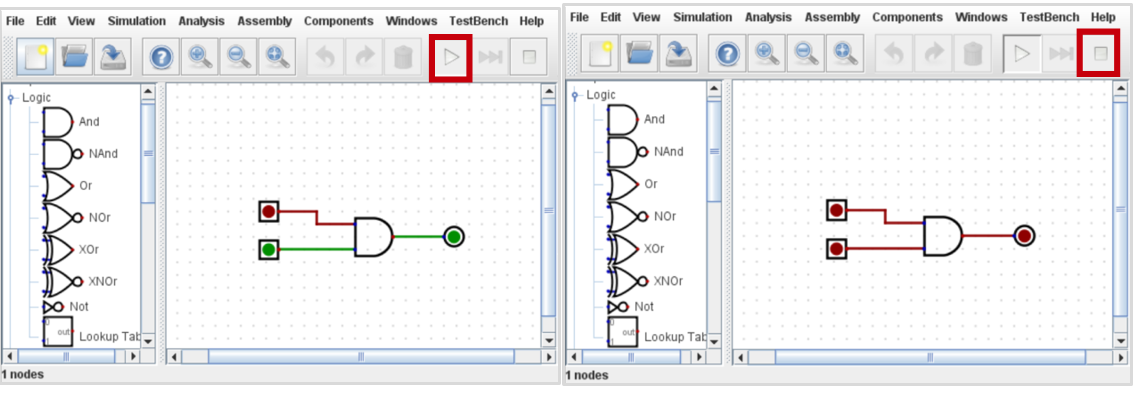

如左下图所示,把交叉的连线删除后,重新连接两个输入端、And元件与输出端。然后点击红圈指明的仿真开始键,可以看到与门电路的运行状态:红色表示高电平,绿色表示低电平。如右下图所示,鼠标在输入端点击,可以翻转电平,使得两个输入端都是高电平(红色),则And元件的输出端变成高电平(红色)。仿真过程中不允许修改电路和增删元件,必须按下红圈指明(右下图所示)的仿真停止键■才能恢复正常模式,修改电路。

小技巧:在非仿真模式下,界面空白处鼠标右键点击按住,可以移动整个界面!在仿真模式下,界面空白处鼠标左键或右键点击按住,都能移动界面!界面的放大或缩小可以借助鼠标滚轮实现!

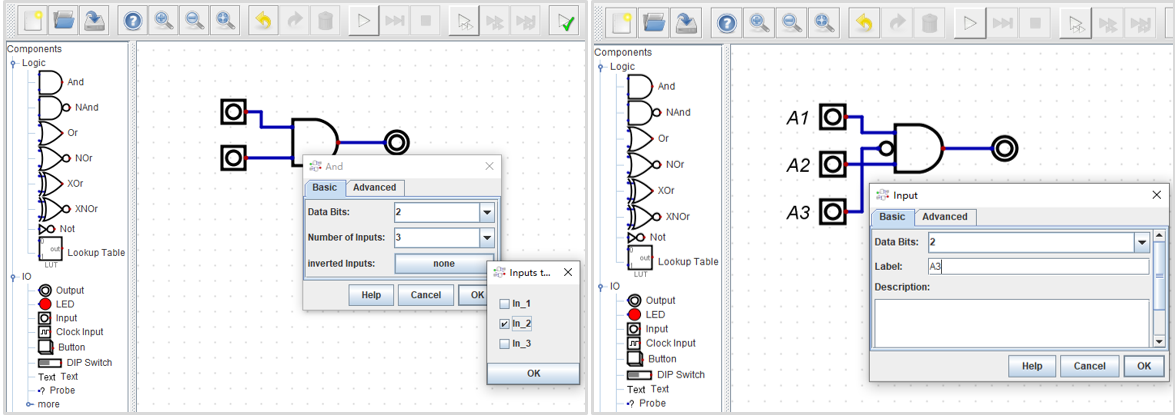

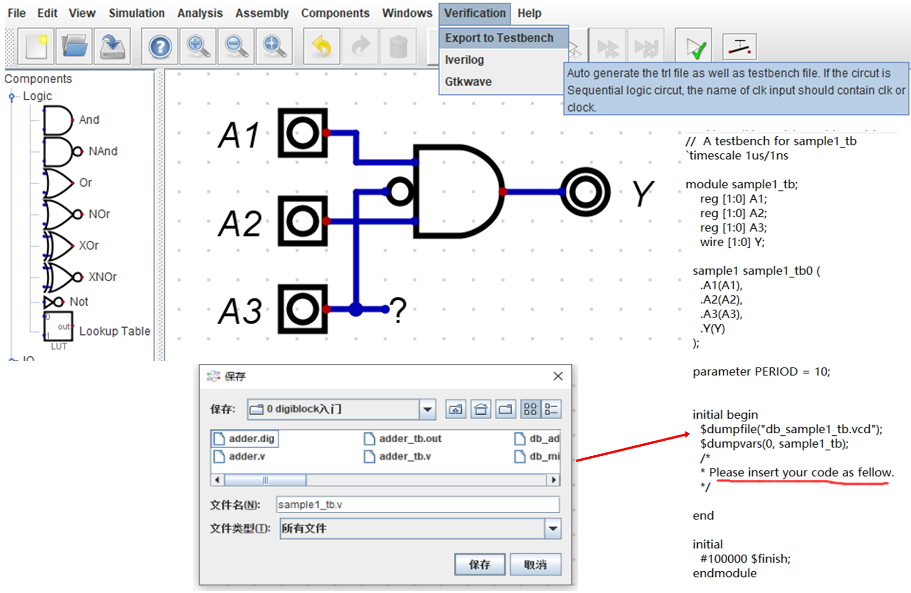

所有元件可以鼠标右键点击打开配置框Basic,如左下图所示,与门And的配置框Basic可以选择元件处理数据的位数Data Bits(图中设置是2位与门),元件输入端Input数目(图中是3输入与门),以及需要反向的元件输入端(Inverted inputs旁边方框左键点击可打开子菜单,勾选对应的输入端即可设置其反向,图中设置的是与门输入端2反向)。

如右下图所示,And与门电路已经被设置为三输入与门(输入端2反向);输入端口Input和Output也可以右键点击打开配置框Basic,右图中输入端口Input可以选择端口的数据位数Data bits以及端口名称Label。注意:相互连接的元器件(例如图中的门电路,输入和输出端口)的Data bits必须一致,才能互相连线。否则会报错。输入和输出端口的Label也必须设置,否则电路工程无法转换成Verilog文件。

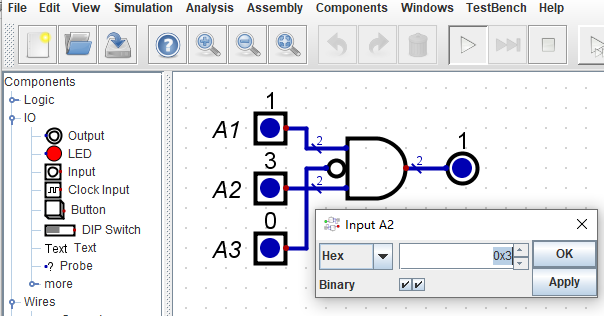

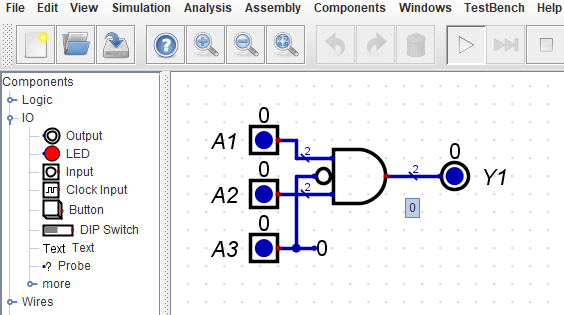

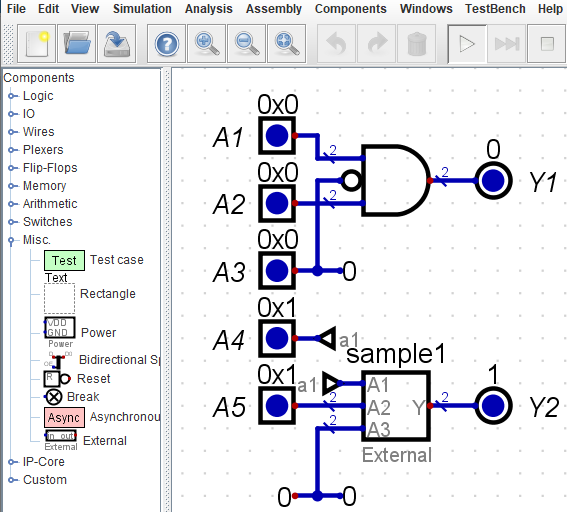

如下图所示,三输入端与门电路设置好后,开始仿真。此时,输入端,连线和输出端的颜色是蓝色,代表此时连线是多位总线,连线上的斜杠数字“2”代表了总线的位数是2bit。此时,右键点击Input端A1,打开的对话框里可以通过多种进制的方式实际输入数值,也可以✔下面的方框图形化选定输入端的数值。下图中,A1=01,A2=11,A3=00,Y1=A1&A2&(~A3)=11。

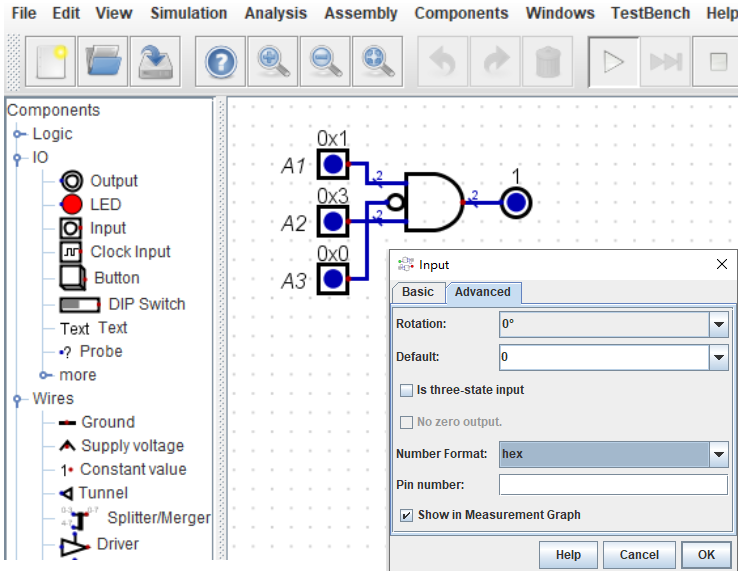

Input输入端和Out输出端的配置框Advance页面,不仅可以选择Rotation元件摆放方向,上下左右旋转元件,方便连线。还可以选择NumberFormat数值进制(默认十进制显示,下图中改为十六进制Hex),Input输入端还可以设置Default初始值(默认初始值为0)。下图中,输入端全部改成十六进制hex显示,而输出端依旧是默认十进制显示。

如下图所示,在Input端A3和And与门的连线上接了一个探针Probe,在仿真的时候Probe会固定给出总线上的当前值,非常有用。当然,也可以鼠标放在总线上显示当前总线上的值(如右下图鼠标放在And与门和Output端Y1的连线上),但鼠标离开总线后数值会自动消失。

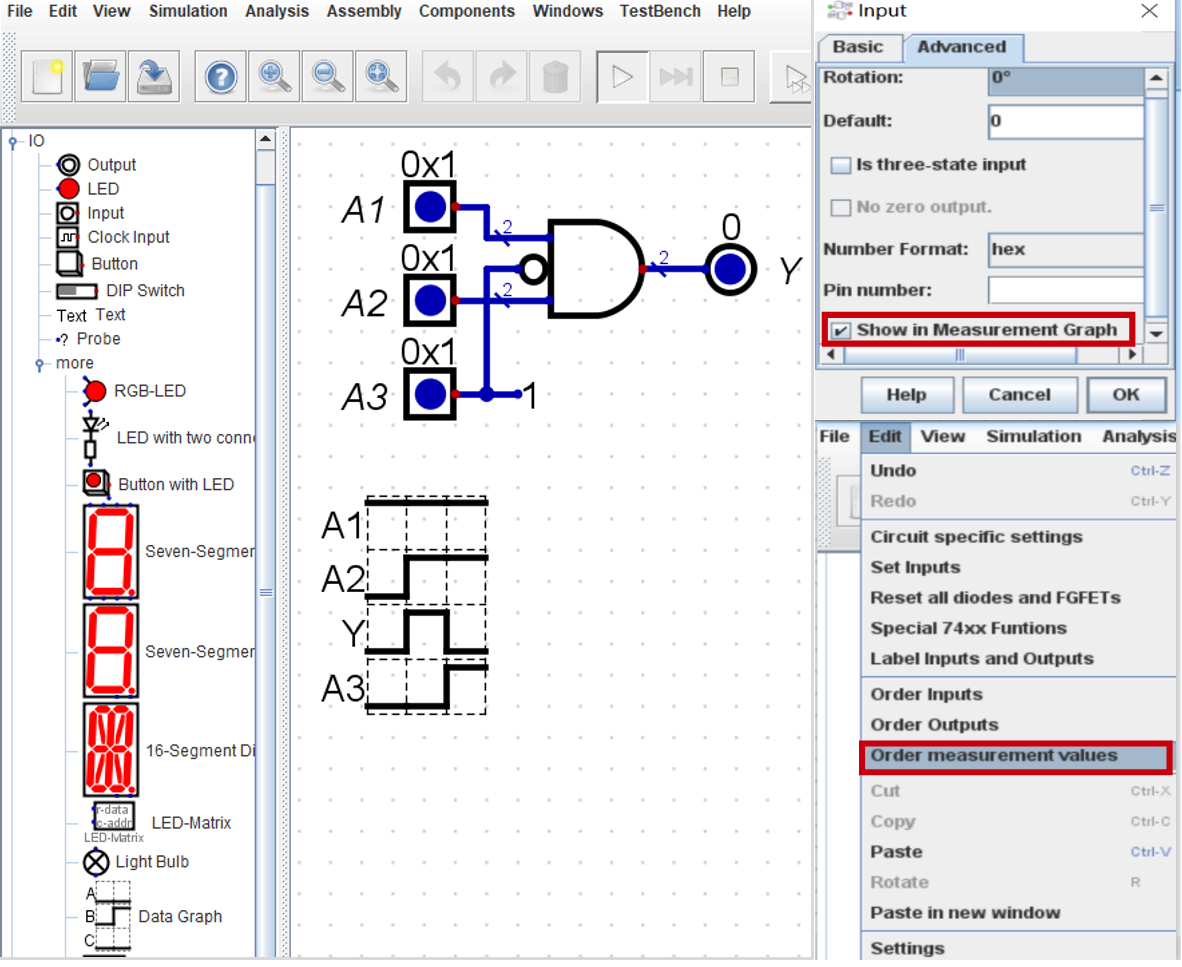

如下图所示,用户可以取出左侧Components树状图的IO节点下的more子节点展开后的DataGraph元件,以便在仿真电路的时候查看测试波形图。电路仿真启动后,输入端(A1,A2,A3)依次为(1,0,0), (1,1,0), (1,1,0);可以依次看到波形图中输入端A1,A2,A3和输出端Y(0, 1, 0)的电平变化情况,达到类似示波器的效果。每一个输入端,输出端和探针Probe都可以在鼠标右键点击弹出的配置框Advanced内选择是否在MeasurementGraph中显示该端口的值。同时,在菜单Edit下的Order Measurement Value选项可以调整测试波形图的端口显示顺序,比如可以把显示顺序从上到下调整为:A1->A2->A3->Y。

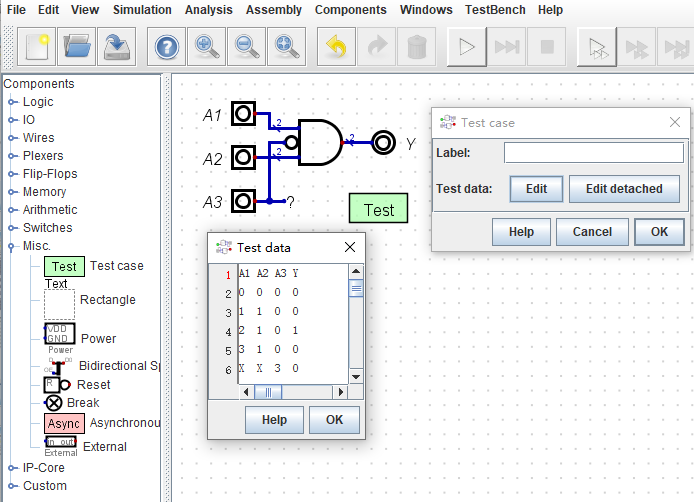

Digiblock允许用户建立测试用例来测试电路,如下图所示:选取左侧Components树状图的Misc节点下的Test case元件,在元件图标上鼠标右键点击可以打开配置框,除了Label命名外,还可以左键按下Edit,弹出Test data框,在框内填写测试用例,然后按OK保存。

上图所示是最常见的测试用例:第一行分别写上输入端和输出端变量(以空格区分),然后第二行开始,每一行是一种状态:列举的输入端变量的取值为条件,以及经过电路后输出端变量的输出值为结果。数值之间以空格区分,而且每一行的数值顺序严格与第一行的变量顺序对应,即变量与数值是一一对应的。输入端的取值除了十进制常数以外,还可以取值“X”和”C”:”X”表示该变量无论取何值,都不影响该变量所在行的其他变量的数值;“C”表示该变量不是以静态数值为条件,而是以上升沿跳变(0->1)触发为条件。而输出端除了十进制常数以外,还可以取值“Z”,表示该输出端在此行状态下输出是高阻。

上述测试用例的问题是需要使用者逐一列举所有可能的值,有可能有遗漏(例如上图中的测试用例就没有包括所有可能出现的状态,尤其是A3≠0的状态)。还有一种自动生成测试用例的方法是向量取值repeat(n),如下所示:n表示总共有n行,每一行n的取值从开始的0到结束的n-1. 每一行状态中,(vlue)表示与第一行的变量一一对应的数值。注意:状态行(从第二行开始)中,除了常数以外,所有变量n及其表达式都必须用()圈起来。

A1 A2 A3 Y

repeat(16) (n>>2) (n&3) 0 ((n>>2)&(n&3))

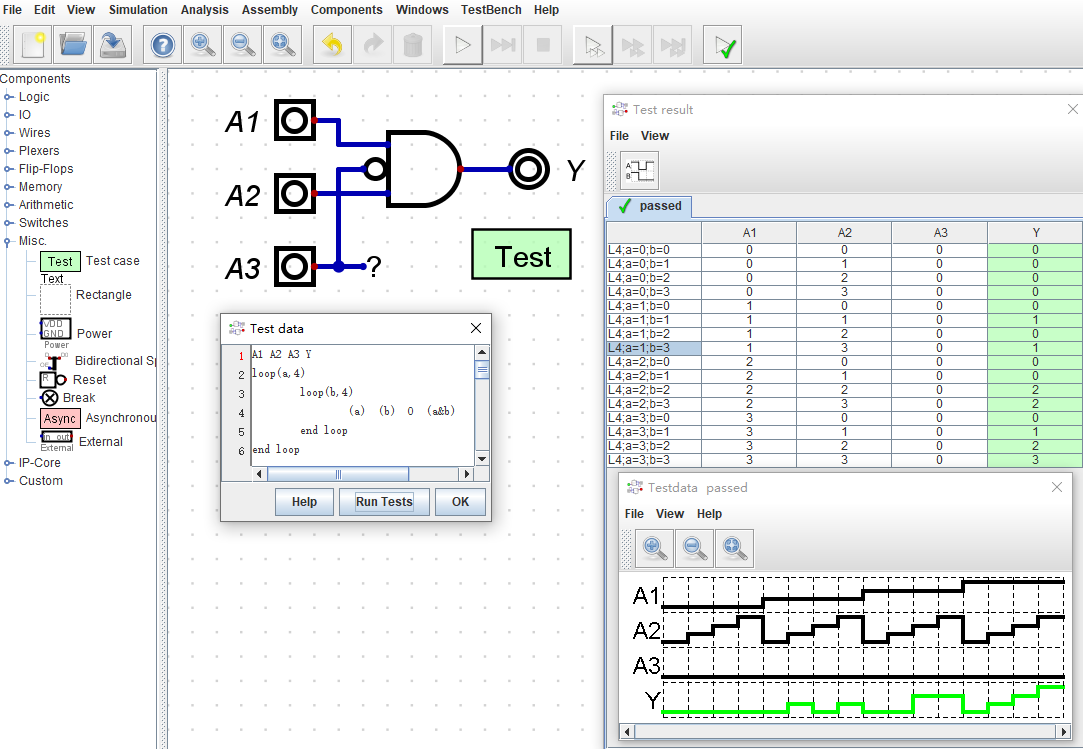

与repeat相似的另一种测试用例自动化方法是loop循环,遍历所有可能状态:变量a为大循环,b为小循环,每个循环都遍历4种状态,总共有4*4=16行状态。

A1 A2 A3 Y

loop(a,4)

loop(b,4)

(a) (b) 0 (a&b)

end loop

end loop

在loop循环中,如果不需要遍历所有状态,可以采用随机值random(i),例如以下只随机列出了10种状态(注意,random(i)的值可能超过A1/A2位数,则赋值时只有与A1和A2相等的低位数保留下来):

A1 A2 A3 Y

loop(i,10)

let a = random(i);

let b = random(i);

(a) (b) 0 (a&b)

end loop

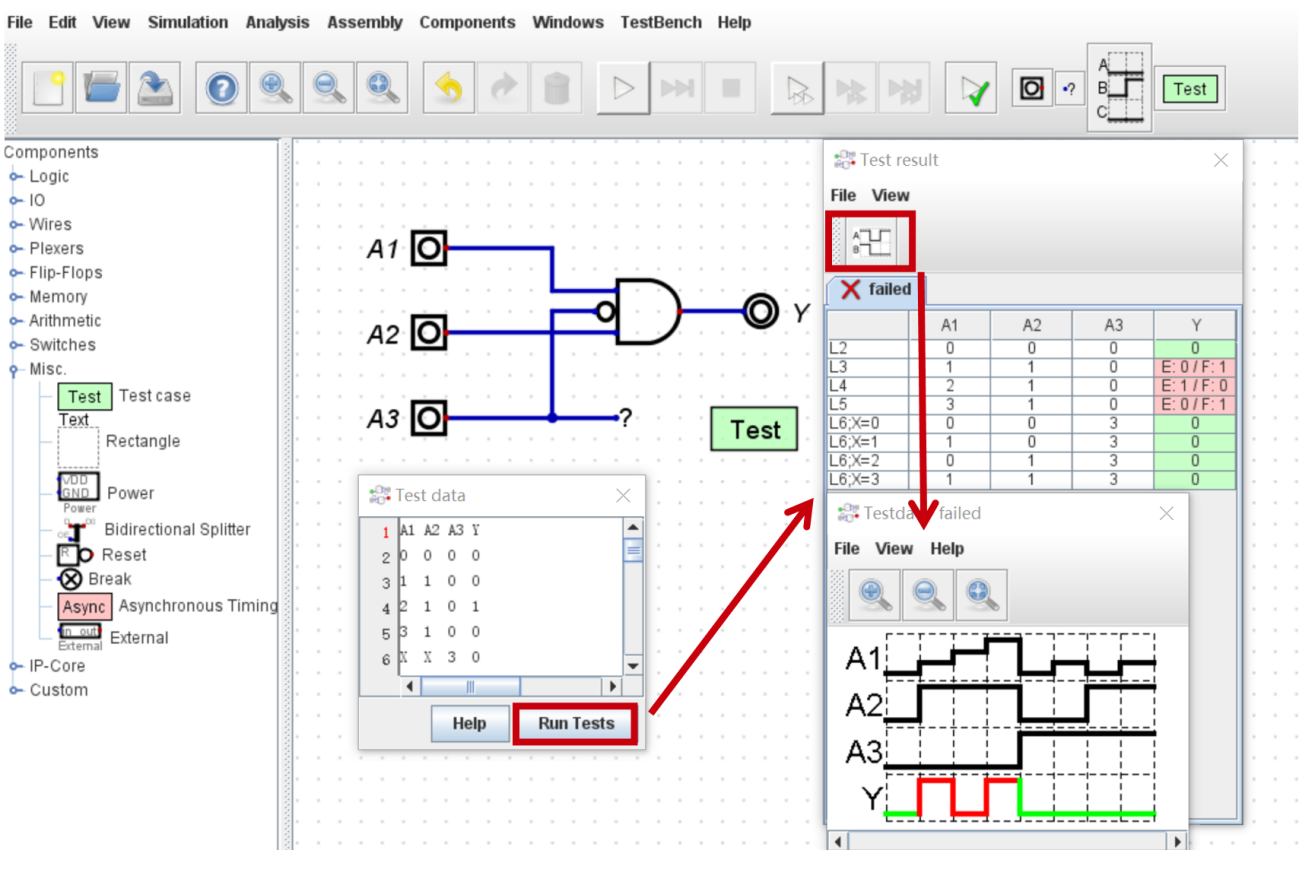

如下图所示,在Test case元件图标上鼠标右键点击可以打开配置框,再左键点击Edit detached,弹出Test data框,点击Run Tests,可以看到测试用例运行结果(Test result):其中输出端Y的绿色部分表示实际电路运行结果与Test data保持一致;而红色部分表示不一致,其中“E:”表示Test data中约定的输出值,而“F:”表示实际电路运行的结果。

此外,还可以点击Test result列表上方的绘图按钮,给出类似DataGraph的表格,其中红色线和绿色线表示实际电路与测试用例有差异的状态,与Test result列表中红色和绿色区域对应。

Test case测试用例的主要用途是老师可以用来快速校验学生的电路是否正确:例如构造一个理论推导正确或根据参考电路推导的Test case测试用例,然后放入被测试的电路执行。若提示出错,将可以清楚看到在输入端什么状态下,输出端会出错(F:),正确的输出应该是多少(E:)。

下图所示则是采用自动测试用例与上述电路实际完全一致的情景:

下图所示则是采用自动测试用例与上述电路实际完全一致的情景:

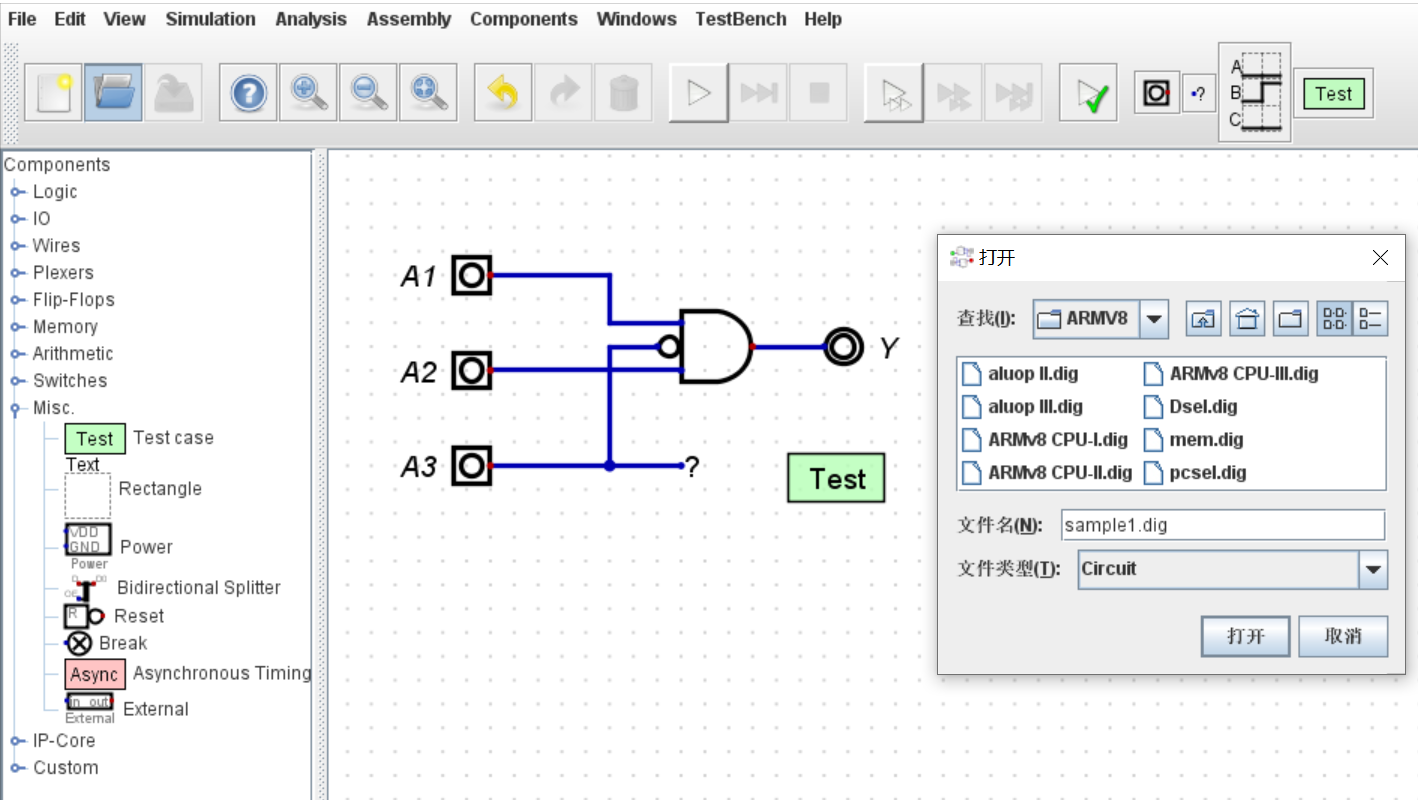

如下图所示,设计和测试好的电路,需要及时点击保存按钮到指定文件夹。下图中,电路被命名为sample1.dig,保存在ARMv8文件夹内。所有Digiblock电路工程文件的后缀都是.dig。

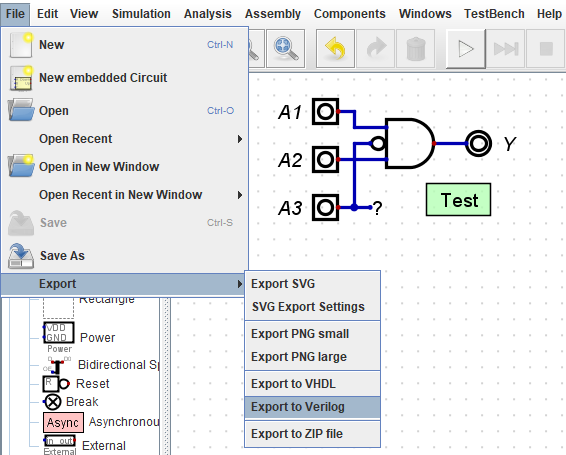

如左下图所示,sample1.dig工程保存好后,可以选择菜单栏里File菜单内的Export子菜单,选择输出Verilog文件或VHDL文件。例如点击Export to Verilog,从dig工程的电路转化成的Verilog代码如右下图所示。

注意:可以生成Verilog文件的电路中所有端口必须命名,并且电路不能包括button按键或LED灯等没有Verilog代码对应的元件,否则会报错。此外,电路中所有元件最好命名,否则系统会自动取名。

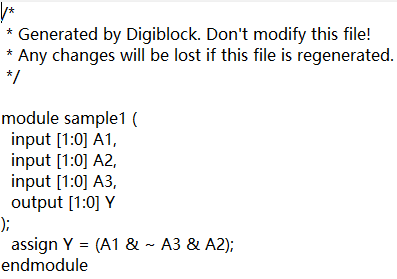

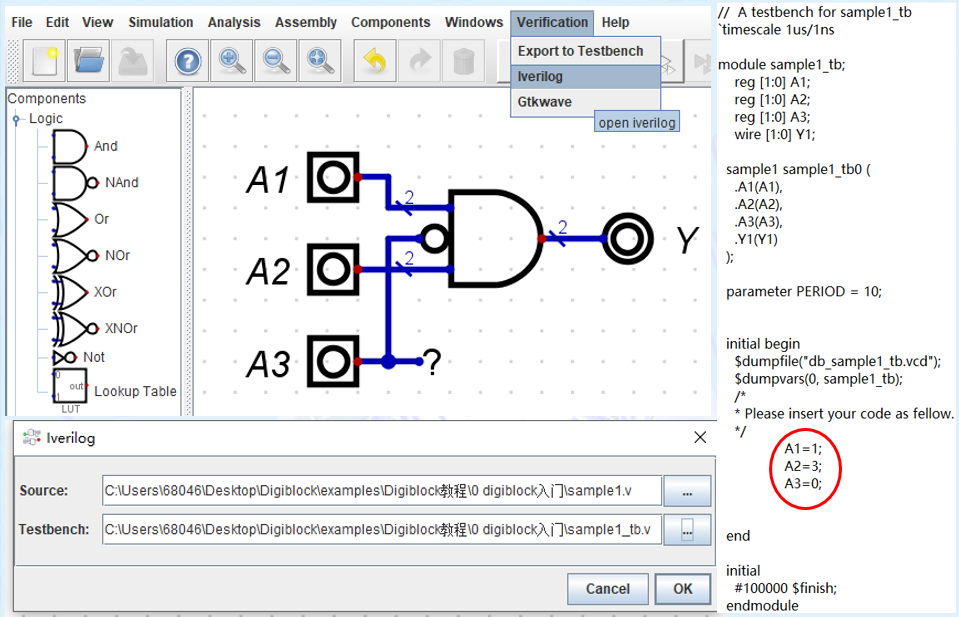

如下图所示,sample1.dig对应的Verilog文件sample1.v生成后,才可以通过菜单栏里Verification菜单内的Export to testbench选项,生成当前sample1.v对应的Testbench模板,如右下图所示。该模板中需要用户自行设计和添加测试所需的激励代码。

注意: dig工程转换的Verilog文件命名为xxx.v,则对应的Testbench模板命名必须是xxx_tb.v,如下图所示的sample1.v和sample1_tb.v。此外,dig工程的时钟端口必须命名为clock或clk。

如右下图所示,Testbench模板添加测试激励代码后,选择菜单里Verification菜单的iverilog选项,在Source和Testbench菜单栏中分别选择xxx.v及其Testbench模板xxx_tb.v,如左下图所示。按OK后,在当前目录下生成db_xxx_tb.vcd波形文件。

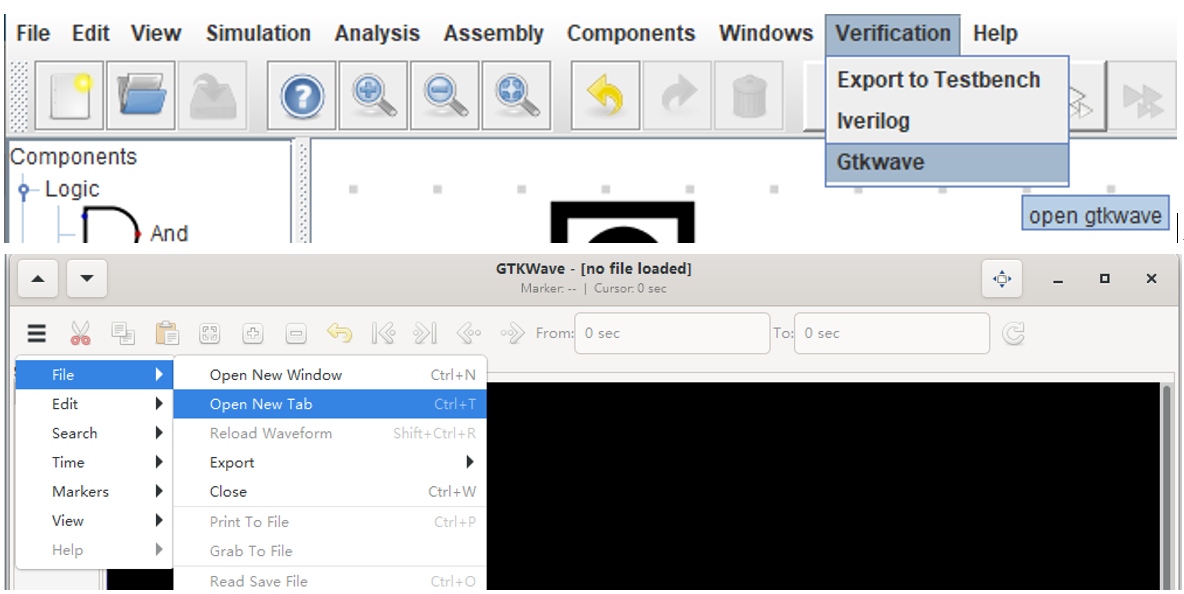

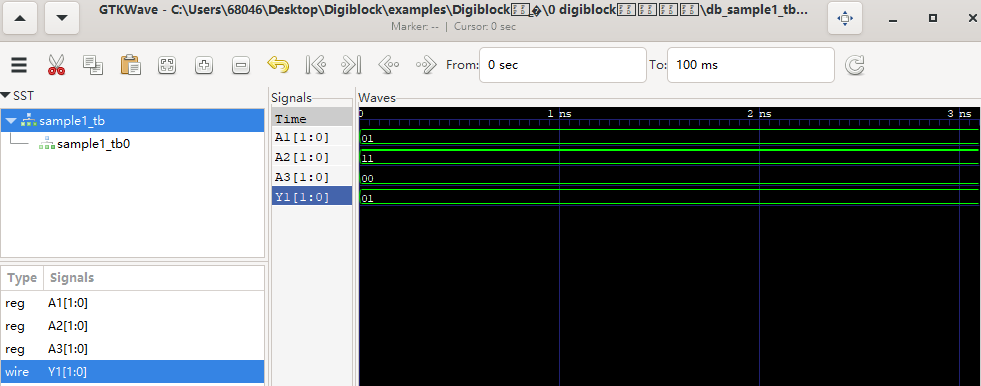

如下图所示,db_xxx_tb.vcd波形文件生成后,可以选择菜单里Verification菜单的GTKwave选项,打开GTKwave页面。选择其左侧菜单栏的File菜单里的Open New Tab选项,打开已经生成的db_xxx_tb.vcd波形文件,可以观察到在用户指定输入()下的电路仿真输出结果。

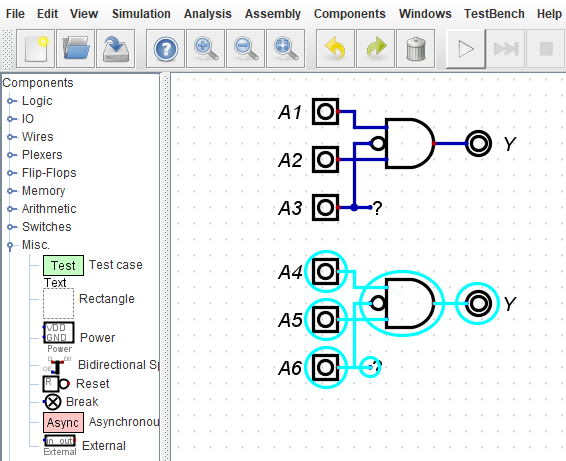

倘若sample1.dig中需要增加一个类似的三与门电路,不需要重复上述绘制电路过程,只需要鼠标拖动形成虚线框选中整个电路后,使用快捷键Ctrl+C复制,再快捷键Ctrl+V粘贴,则会出现一组被蓝色圈住的元件,随鼠标移动。鼠标在指定位置空白处左键点击即可安置第二个三与门电路。其中,如果被复制的电路中端口已经被命名,则复制出来的电路中的端口会顺延(例如下图中输入端口Ax,有数字标号所以顺延)或者保持一致(例如下图中输出端口Y)。复制和粘贴不仅在同一个dig电路中使用,还可以在不同dig之间复制粘贴电路。

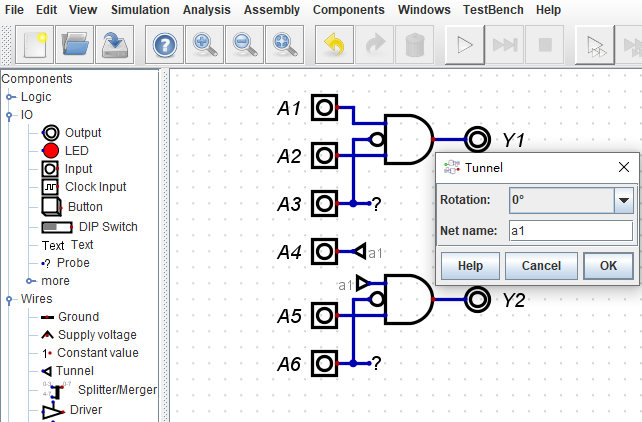

如左下图所示,把两个三与门的输出端分别改为Y1和Y2(同一个电路中不允许有重名的输入端和输出端,否则导出Verilog文件会报错)。除了连线,还可以使用左侧Component树状图的Wires节点的Tunnel元件把两个元件“飞线”连接起来,起到连线的作用,可以在复杂电路中大大化简连线的数量。如左下图所示,第二个与门的A4与And元件的连接改为Tunnel “飞线”。鼠标右键单击Tunnel可以打开配置框,其中Net name必须命名,因为同名的Tunnel等同电气连接。

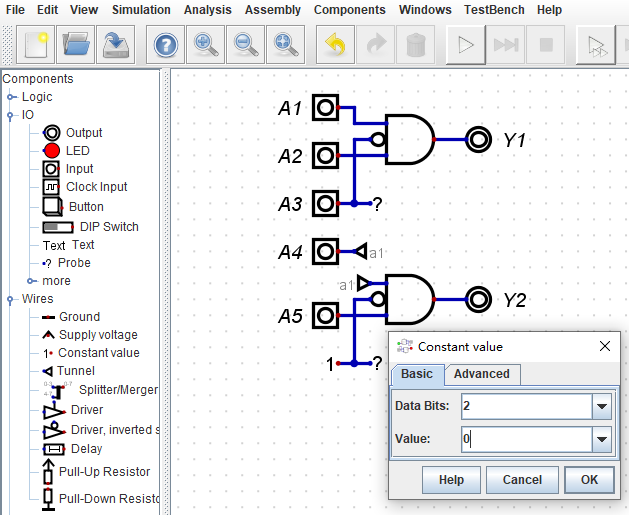

如右下图所示,除了输入端Input可以手动设置输入值以外,可以使用左侧Component树状图的Wires节点的常数元件(Constant value),该元件在仿真全过程中不许改变数值。鼠标右键点击打开常数端的配置框Basic,可以选择常数的位数Data Bits和数值Value(注意:常数端的位数Data Bits也必须与其连接的元件端保持一致),也可以与输入端Input,输出端Output一样,在配置框Advanced页面修改Rotation元件摆放方向和Number Format数值进制。

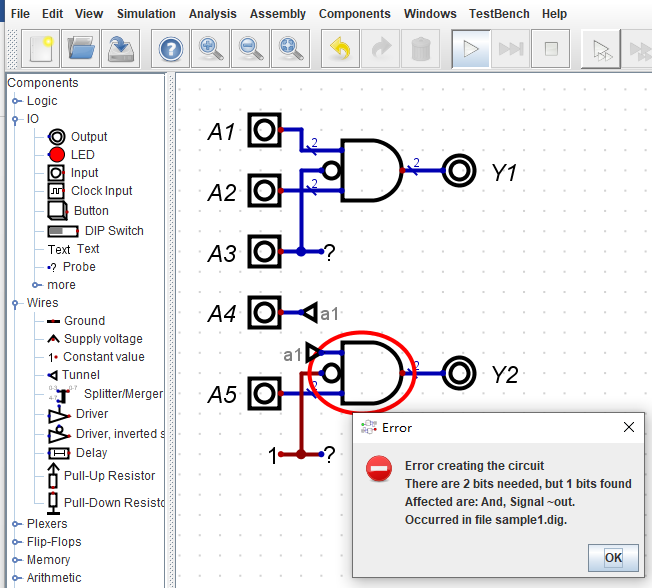

注意:常数元件的位数Data Bits必须与其连接的元件端保持一致!所以引入常数元件(Constant value)后,必须配置位数,否则会出现以下情况报错:发生错误的位置是红色圈起来的元件或该元件相连的其他元件(下图所示错误就是发生在常数“1”的位数与与门不一致)。Error框内提示:正确的方式应该是2bit端口(或连线),目前出现的是1bit端口(或连线)。根据Error提示信息,用户可以有效定位仿真错误所在之处。

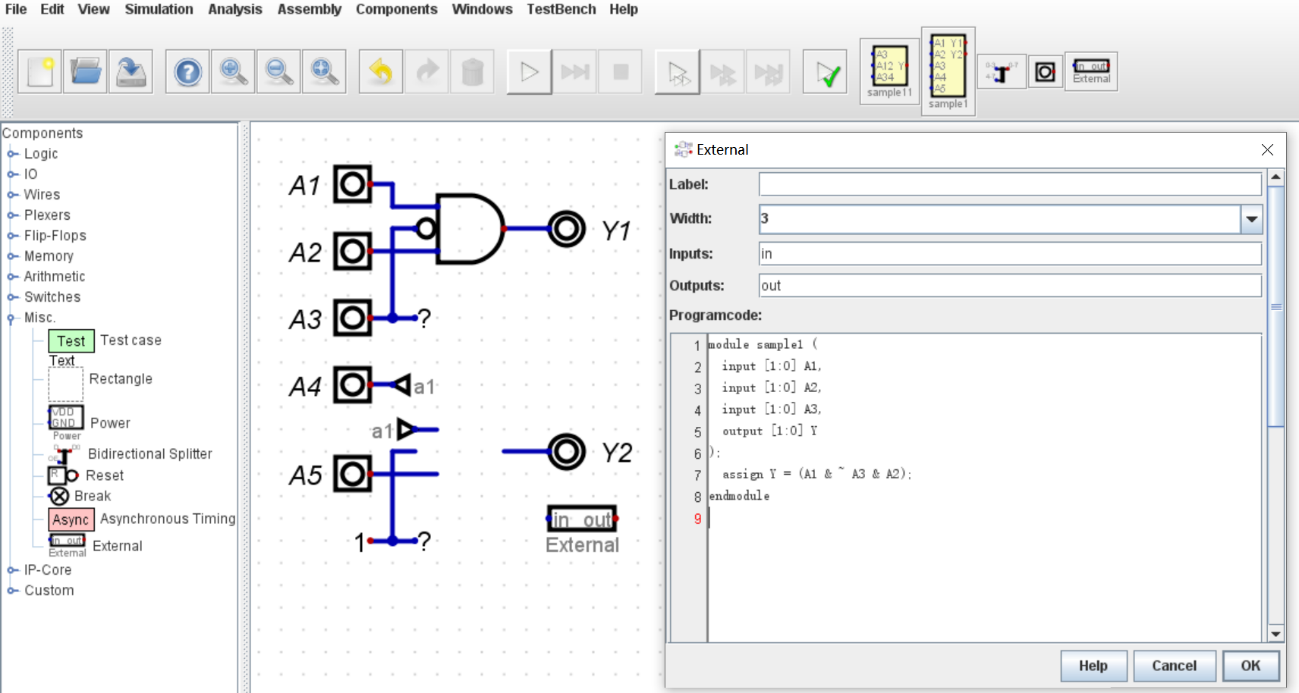

Digiblock不仅可以图形化搭建电路结构,还可以与Verilog代码混合仿真!例如下图所示,选用Component树状图的o-Misc节点下的External组件,右键点击打开配置框。在Programcode框内输入VHDL/Verilog代码,图中把前面生成的v文件重新复制进去。然后,Application框内选择编译工具,若Programcode框输入的是VHDL代码,则选择GHDL选项;若是Veirlog代码,则选择iVerilog,然后左键点击check按钮,没有报错信息,则证明输入的代码语法检查通过,可以解析。同时,Label框,Inputs框和Output框会自动代入VHDL/verilog代码中module的名字,输入参数和输出参数,无需手动输入。

需要注意的是,在使用External组件前要确保已经安装成功GHDL或iVerilog开源仿真器,而且在Digiblock的”Edit->settings”路径下的Advanced配置框内已经正确输入了上述开源仿真器的exe文件路径,否则digiblock无法调用仿真器进行检查。

再次声明,在External组件中使用VHDL代码对应安装和Applications选项声明GHDL,使用Verilog代码则对应安装和Applications选项声明iVeilog。

External组件成功配置后,外形会变化,其边框左边出现蓝色端点表示输入端,右边出现红色端点表示输出端。Label自动以module名字命名。将External组件替代原先的第二个3与门,点击运行仿真,如下图所示。External在digiblcok工程里面仿真正常,其功能与内部的Verilog代码符合。

External的主要用途是在digiblock工程内复用第三方的Verilog代码,例如IP资源。Digiblock不排斥VHDL/Verilog代码,可以混合图形化与HDL代码,共同仿真。另一方面来说,Digiblock为Verilog代码提供了一个虚拟仿真环境,可以快速验证代码的功能和正确性,方便Verilog学习。

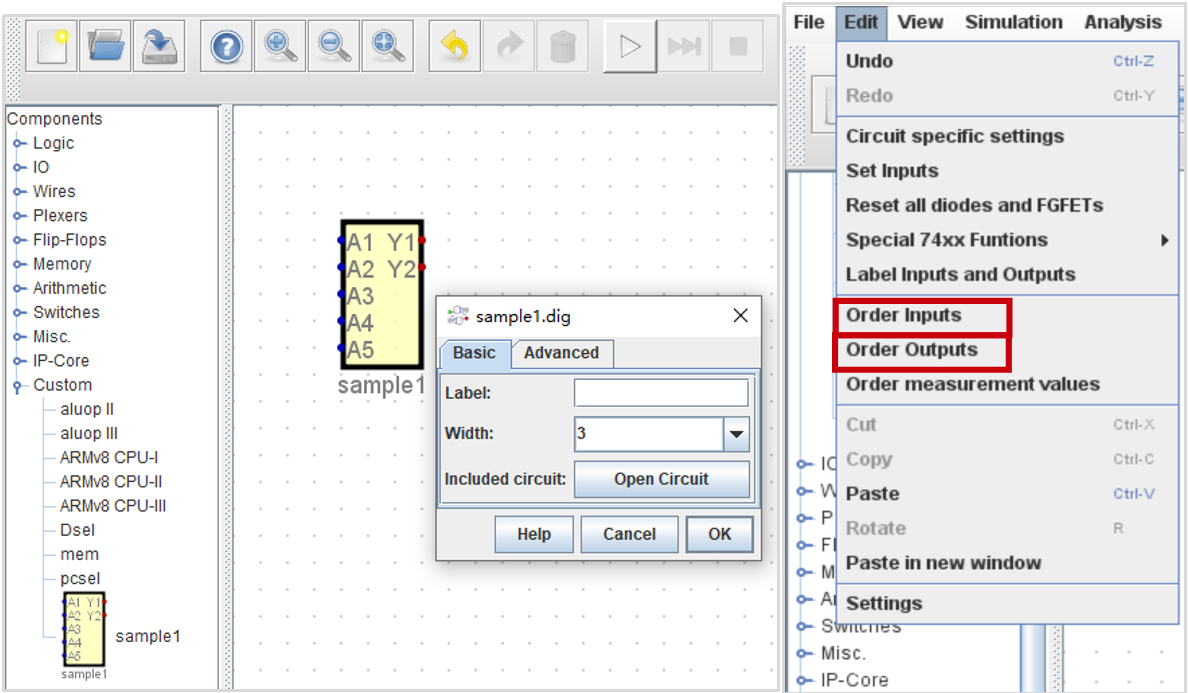

经过上述改动后,保存 sample1.dig。重新创建一个空白dig文件,首先命名为sample11.dig,保存在与sample1相同的文件夹ARMv8路径中。打开sample11.dig,在左侧Component树状图的Custom节点下,所有与sample11.dig在同一文件夹内的dig文件都可以作为子电路模块放在这里,其中就包括了sample1. 如左下图所示,鼠标左键点击Custom节点下的sample1,与选择元件类似,会出现被蓝色框住的子电路sample1随鼠标移动;再次在某个空白位置处左键点击安放好子电路sample1后,鼠标右键点击打开子电路sample1的配置框Basic,可以修改子电路黄色外框的宽度(避免左边输入端和右边输出端的名字重叠),还可以点击Open Circuit打开子电路的dig文件。子电路黄色外框左边的输入端上下排序和右边的输出端上下排序可以通过Edit菜单的Order Inputs和Order Outputs选项来调整,如右下图所示。

注意:工程必须先保存!才能调用文件夹同一路径下的其他工程(dig文件)作为子电路!

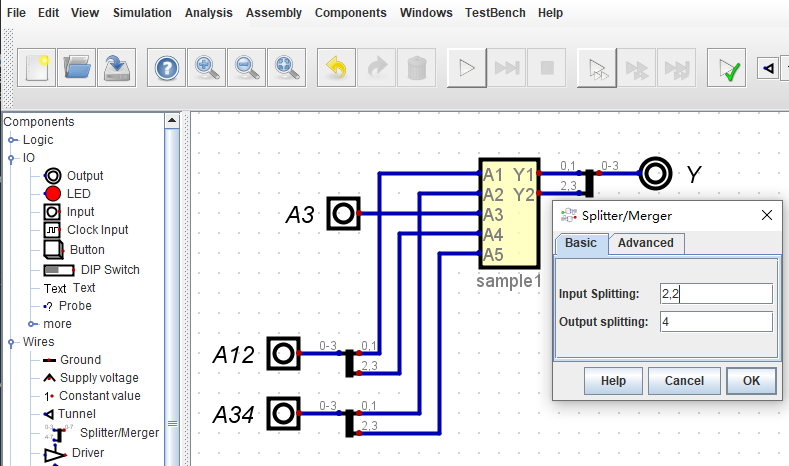

最后,因为A1/A2与A4/A5分别是两个与门的输入端,Y1和Y2分别是两个与门的输出端,所以在sample2.dig中,除了A3采用Input输入端A3以外,其他Input输入端/Output输出端采用左侧Component树状图的Wire节点下的splitter分线器元件,统一连接到两个Input输入端A12和A45上。而输出端Y1和Y2也可以采用splitter元件合并到一个输出端Y上,如下图所示。鼠标在splitter元件上右键点击,打开配置框Basic,可以填写Input splitting和Out splitting的格式,Input/Output splitting的格式可以是单个常数n,表示一个n bit的端口;也可以是m*n,表示是m个nbit的端口(端口平分);也可以是具体的端口号“x-y”,表示从端口号x到端口号。例如下图中右边的splitting元件,Input splitting端连接的是子电路的Y1和Y2端口,Out splitting端连接的是端口Y,所以是一个汇聚端,Input splitting={2,2},表示元件自动从最低端口开始分配两个2bit的输入端;Output splitting=4,表示只有一个4bit的输出端。Input splitting还可以有以下等价的写法:Input splitting={2*2},或者Input splitting={0-1,2-3}。注意:如果写成Input splitting={2-3,0-1},则输入端2-3在上面(与端口Y1连接),输入端0-1在下面(与端口Y2连接)。同理,左下图边的两个splitting元件,是分叉端,其Input splitting=4,Output splitting={2*2}。Splitting元件的设置规则是Input splitting的端口不允许重复,其端口数不能比Out splitting的端口数少,例如Input splitting=4,Output splitting ={0-2,2-2}这样的写法是允许的。但是Input splitting={0-2,2-2},Output splitting =4的写法是错误的,Input splitting不能重复,而且不允许Input<Output。

4.逻辑门电路基础

掌握了Digiblock的基本使用,需要了解逻辑门电路的基础,并且可以通过Digiblock连接电路图进行练习。

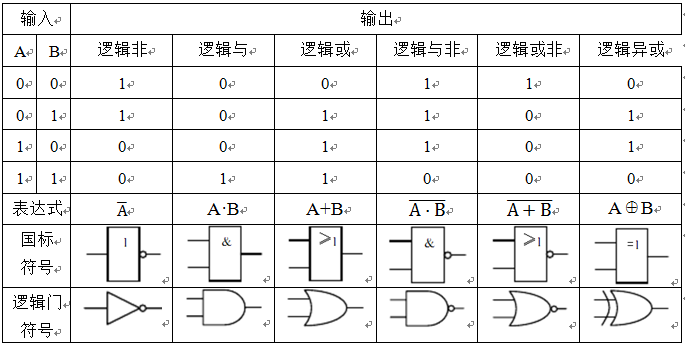

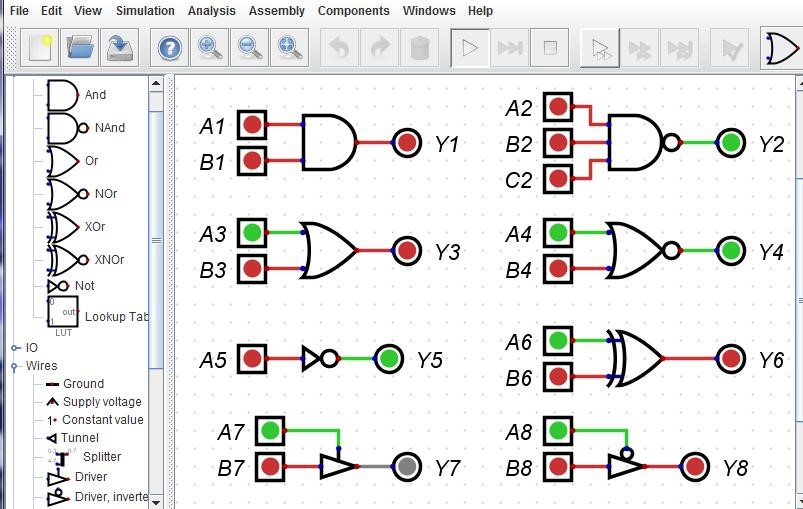

上图为常用逻辑门列表。

logic gate.dig为组合逻辑中常用的逻辑门元件(全部处理的数据位数1bit)。

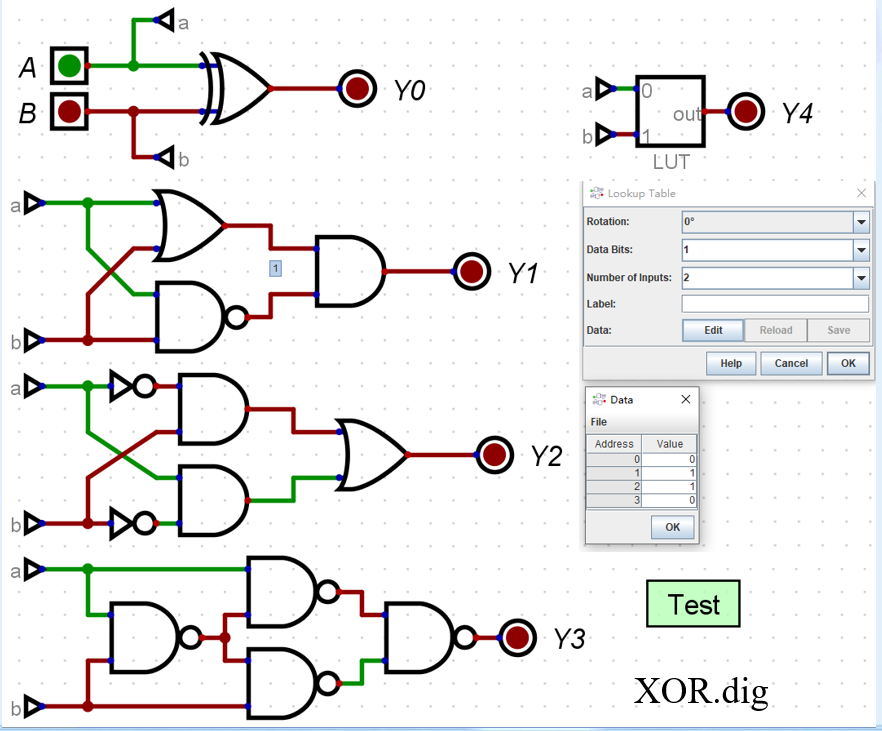

XOR.dig为异或门的门电路和查找表实现形式。

注:组合逻辑电路有两种实现方法:一个是门电路组合实现,多见于ASIC;另一种则由查找表(LUT)实现,多见于FPGA。右键点击LUT,配置框内可以设置输入端口数和输出的数据位数;点击Edit,弹出Data框,可以设定特定的端口输入(即以输入端口为地址)所对应输出的数据。

组合逻辑设计工具:

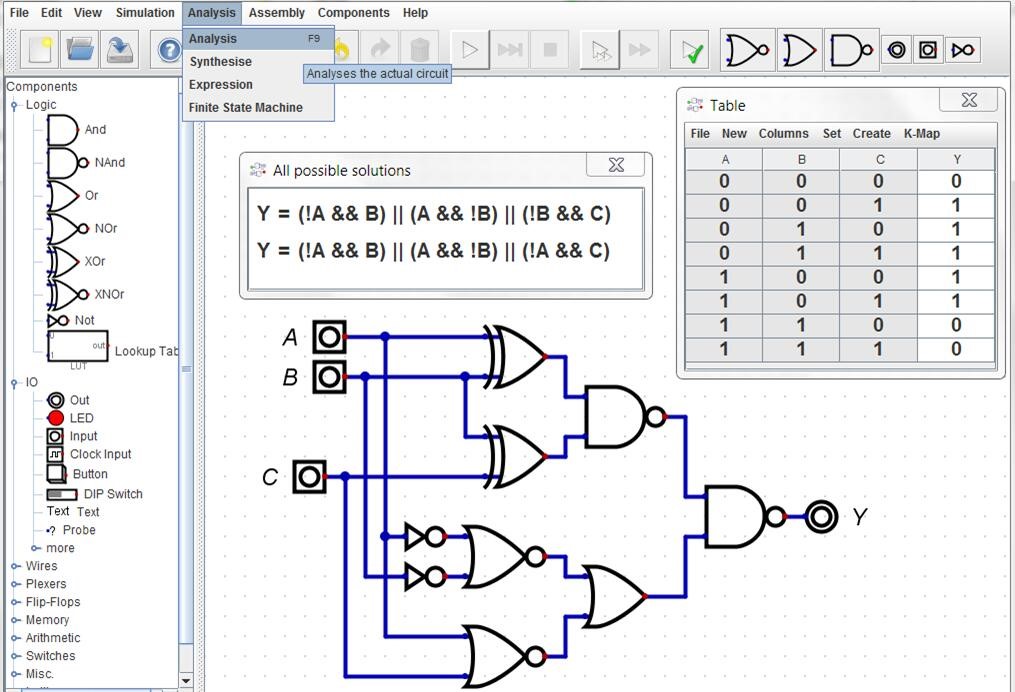

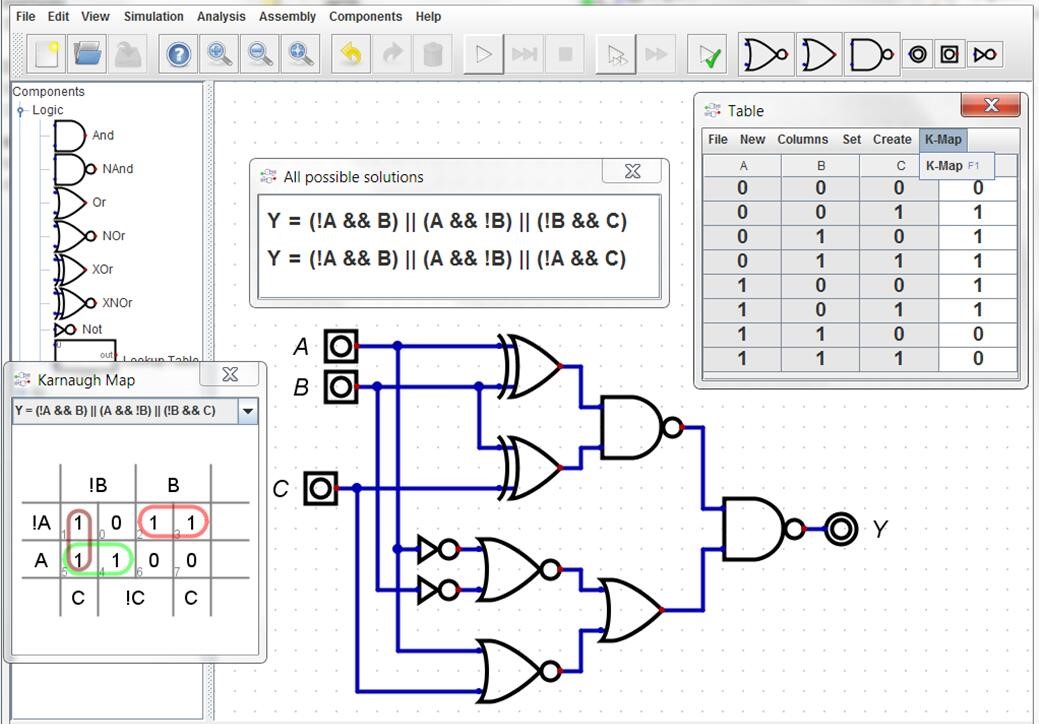

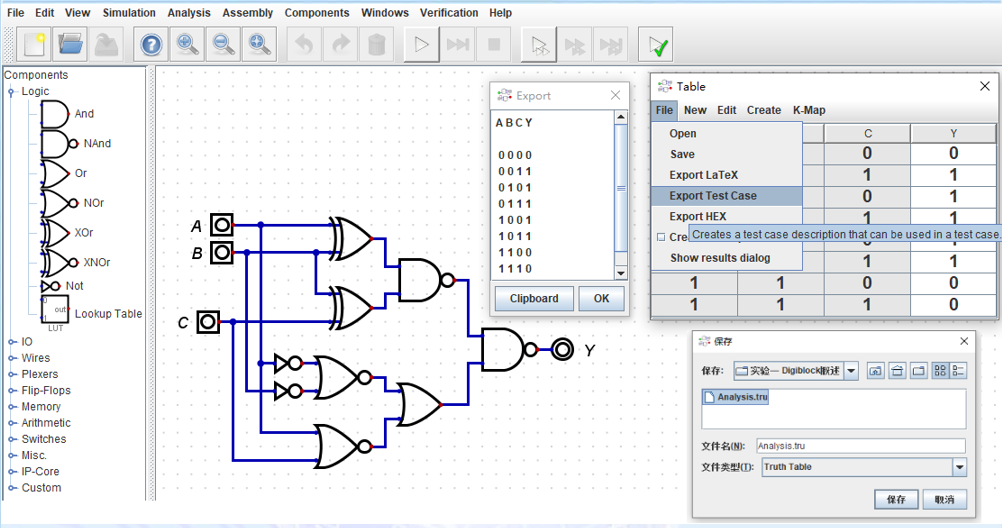

Analysis.dig图。

Analysis功能:对图中的电路自动分析,生成真值表和优化后的多种等价逻辑表达式!

Analysis.dig图。

注:由真值表可以生成卡诺图(K-map),清晰可见逻辑表达式优化的依据(“圈”1)。

Analysis.dig/Analysis.tru图。

注:真值表菜单栏的File菜单里,可以选择Save选项,把真值表以xxx.tru格式保存起来,也可以选择Open选项打开文件夹中的.tru格式的真值表。此外,选择Export Test Case选项,则可以生成符合Test Case要求的测试用例数据,在测试的时候,可使用上述自动生成的Test Case测试用例,考察学生实现的电路功能(输入->输出响应),是否与参考电路的真值表数据一致。

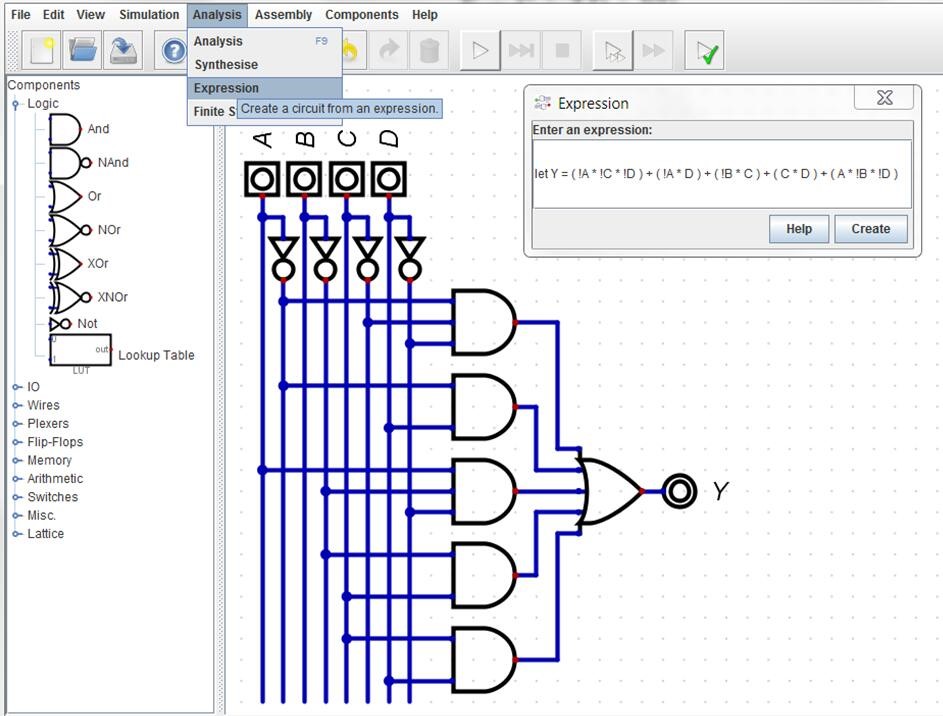

Expression.dig——Expression功能:输入逻辑表达式,自动分析生成电路!

Expression.dig图。

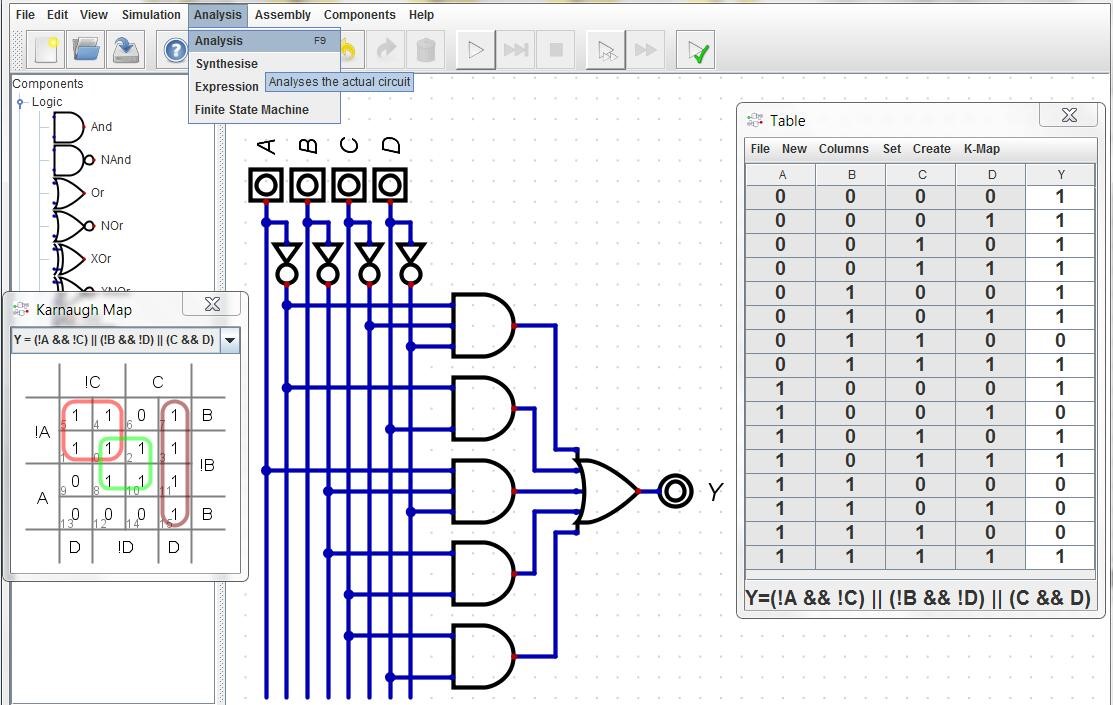

注:对生成的电路再次Analysis生成逻辑表达式,真值表及其卡诺图,与输入的逻辑表达式对照可见,Expression功能生成的电路已经优化,不是简单的逻辑电路翻译。

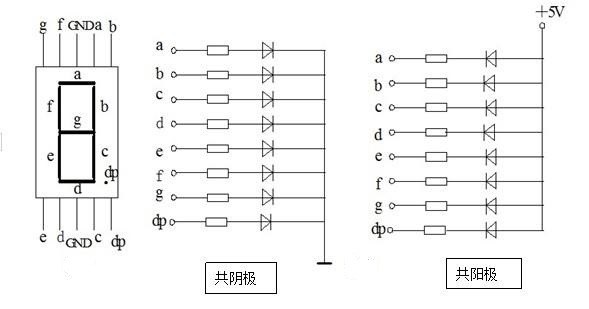

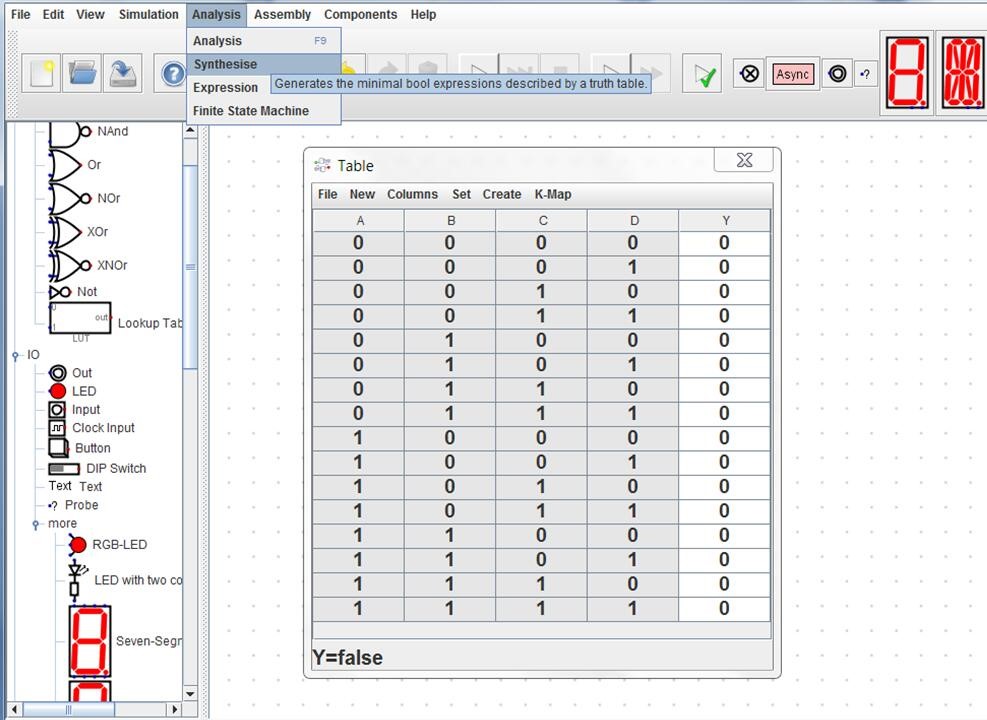

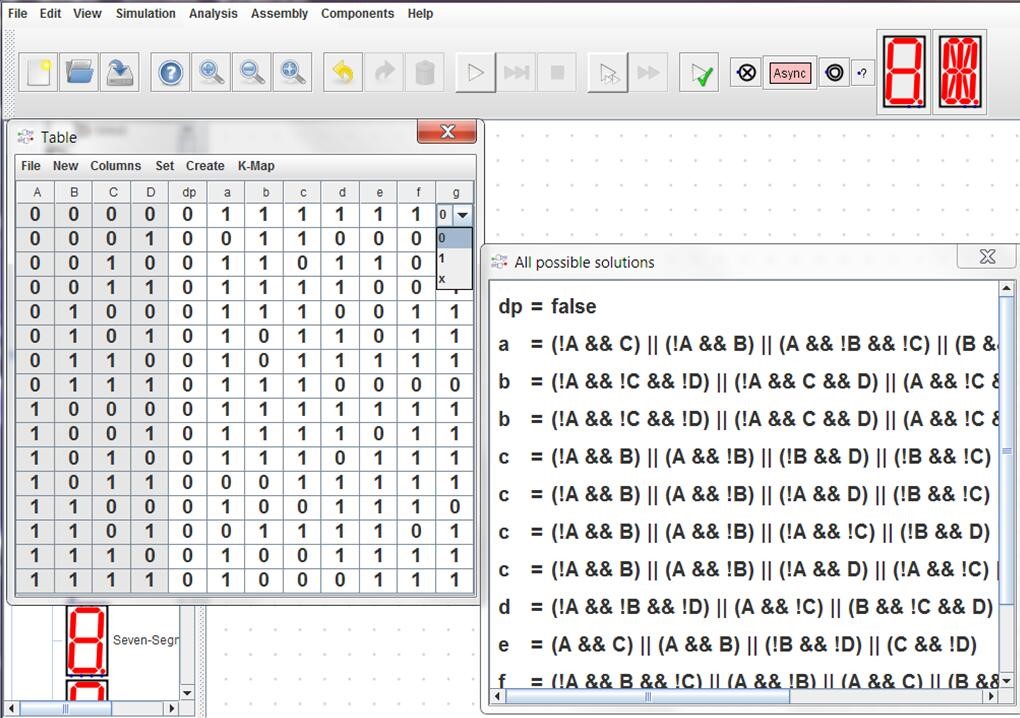

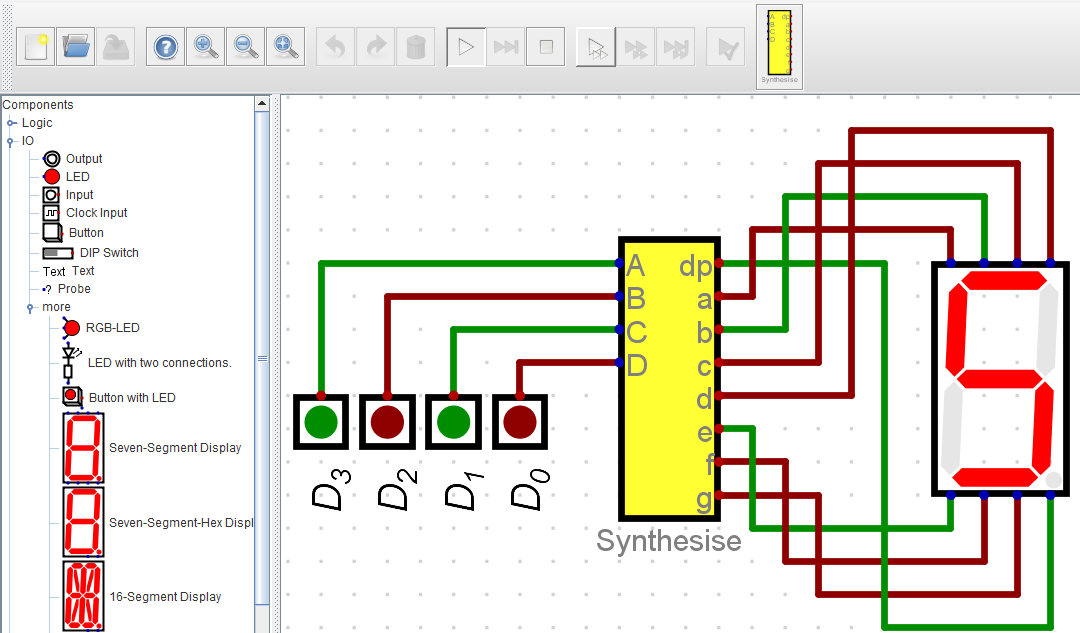

Synthesise功能示例:由真值表生成电路(数码管显示)。

注:七段数码管有共阴极和共阳极两种形式,Digiblock的模型全是共阴极,直接控制。

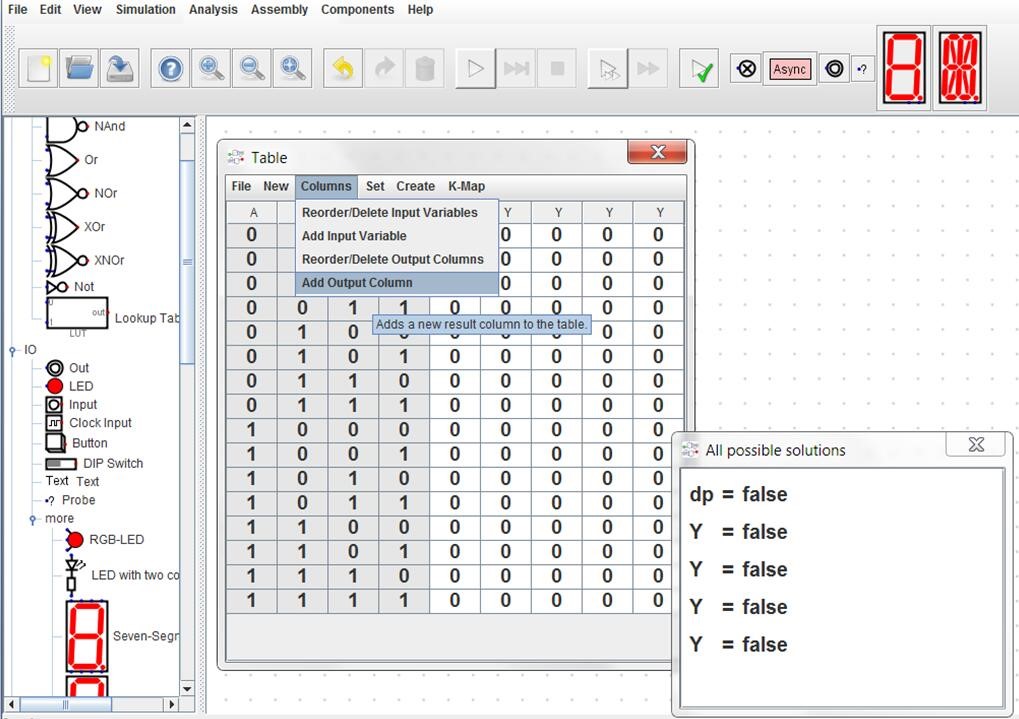

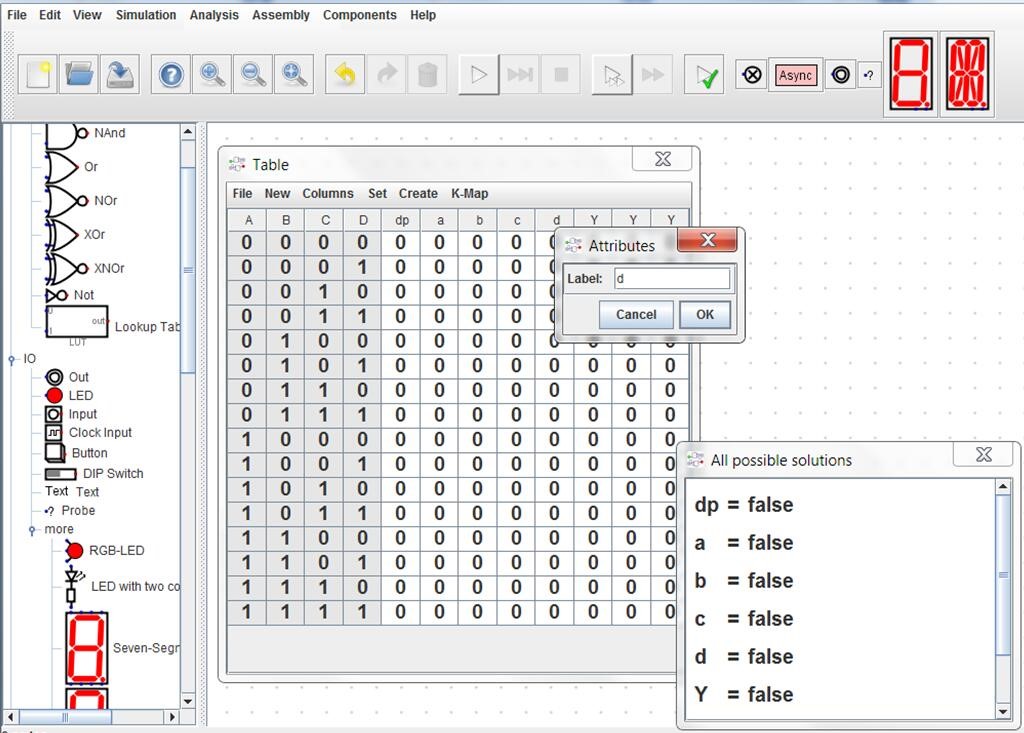

Synthesise功能:建立真值表(或打开已有的真值表)。

注:真值表可以增加输入端和输出端,弹窗可查看逻辑表达式。

注:真值表的输入端和输出端可以任意命名。

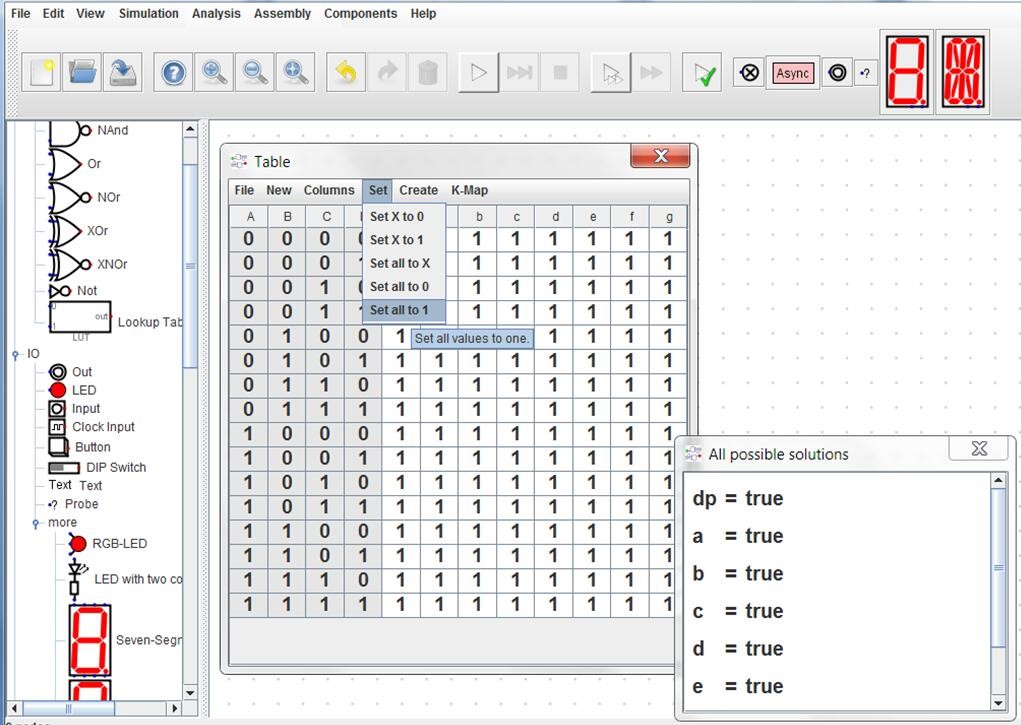

注:真值表可以预置输入端或输出端全部为某个具体值,例如0/1。

注:真值表可以修改输入端或输出端的某个具体值,逻辑表达式会不断跟着修改变化。

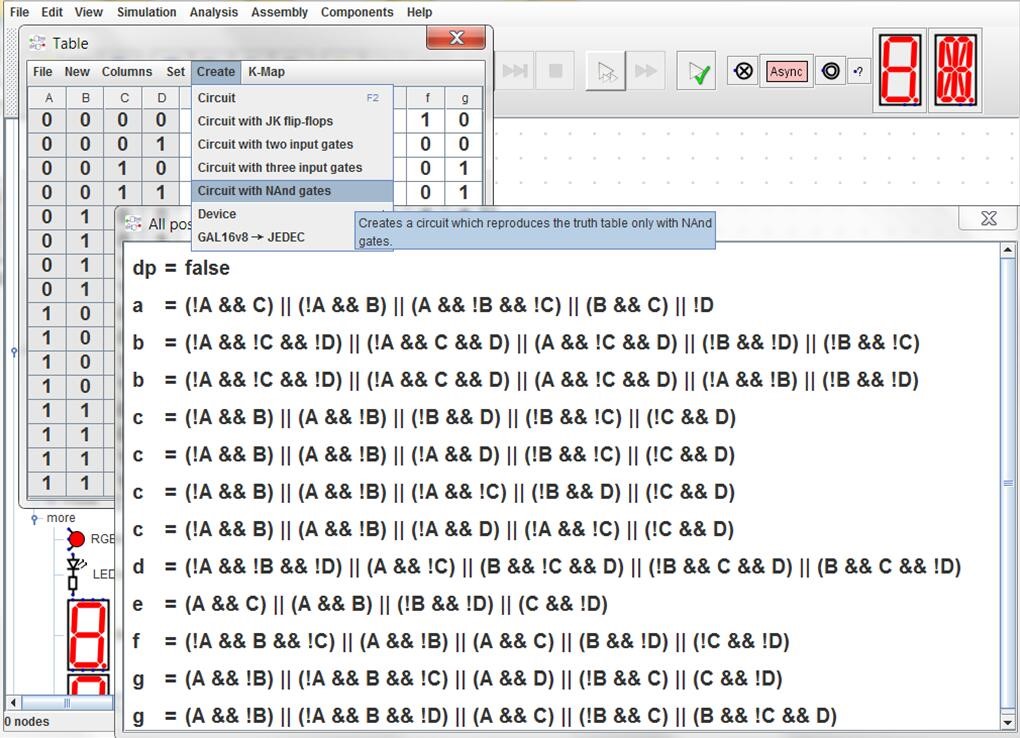

七段数码管真值表及其对应逻辑表达式(注:可以选择生成电路的元件形式)。

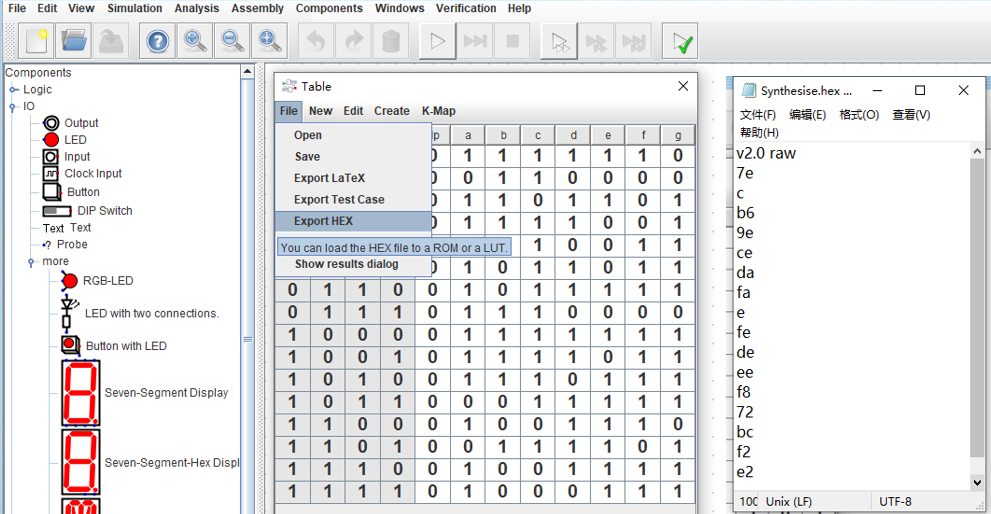

注:真值表菜单栏的File菜单里,可以选择Export HEX选项,把真值表以xxx.hex格式保存起来(即输入值是地址,输出值是数据),如图中所示。该方法可以使用ROM器件或LUT的形式来实现该真值表生成的电路。

注:形成hex文件的时候,输出值的高位->低位顺序是右列->左列,即右边第一列为最高位,左边第一列为最低位!

另:真值表菜单栏的File菜单里的Show results dialog是显示真值表对应的逻辑表达式。

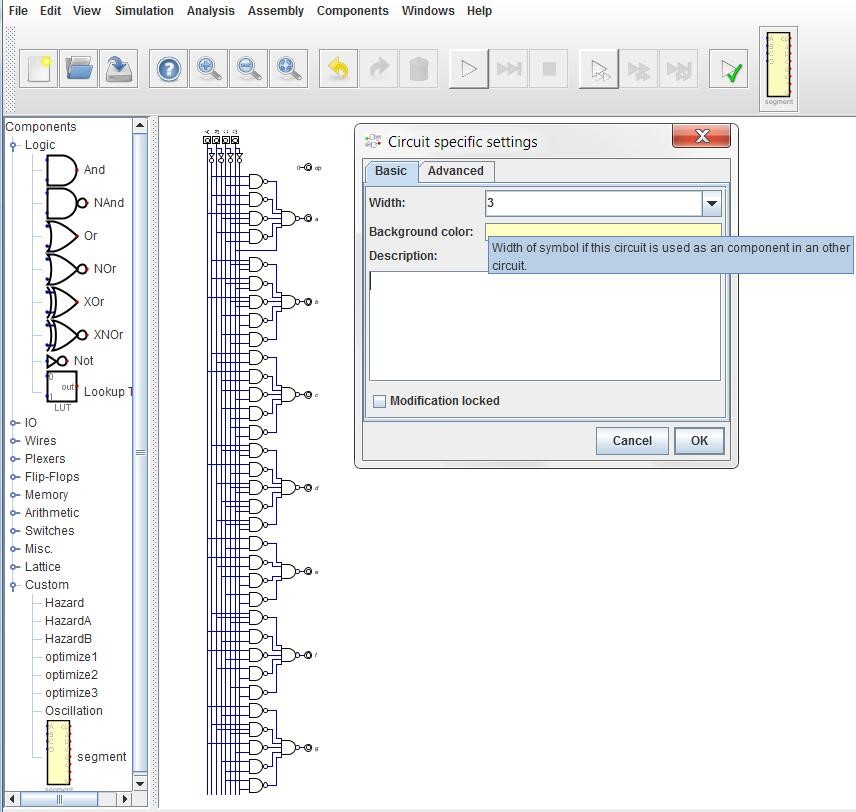

Synthesise.dig——七段数码管的显示电路。

注:真值表生成的电路如左图所示,一般可以作为子电路引入同一个文件夹的其他dig工程中。子电路图标的外形尺寸可以在Edit菜单的 Circuit specific settings编辑默认子电路图标shapes为矩形方框,可更改图标shape外形。宽度亦可设置(以便左右端口名称不要重叠)。

segment.dig——调用七段数码管显示电路(Synthesise.dig)实现的数码管演示电路。

至此本案例,顺利完成!

5.更多学习资源

更多学习内容和资源请扫码报名参加“鲲鹏技术学习加油站”及浏览鲲鹏开发板专区。

1)香橙派鲲鹏Pro开发板技术学习加油站:

2)香橙派鲲鹏Pro开发板专区二维码: