逻辑架构

了解鲲鹏加速引擎上下文逻辑架构,掌握加速原理。

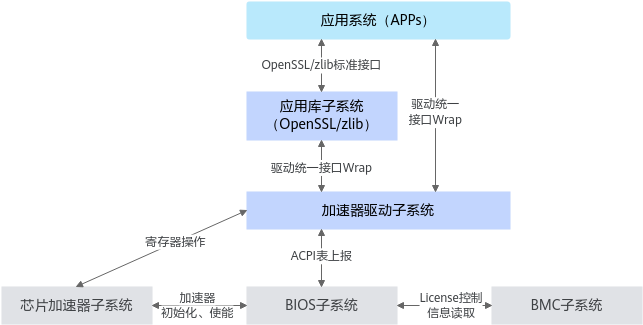

鲲鹏加速引擎系统逻辑架构如图1所示。

各子系统详细功能描述如表1所示,其中芯片加速器子系统、BIOS(Basic Input Output System,基本输入/输出系统)子系统和BMC(Baseboard Management Controller,主板管理控制器)子系统为基于鲲鹏920的硬件服务器自带子系统。

子系统名称 |

功能描述 |

|---|---|

应用系统 |

通过调用应用库子系统或驱动子系统实现对应用加速的功能,包括大数据应用、Web应用等,属于用户层面系统。 |

应用库子系统 |

应用库子系统包括基于OpenSSL加速器引擎、zlib替代库等,向上层提供标准接口。 |

加速器驱动子系统 |

本系统的核心,向上层提供各子加速器模块统一的驱动接口。 |

芯片加速器子系统 |

集成在鲲鹏920处理器中,提供加速器的能力,对上层提供寄存器接口。该子系统是加速器的硬件实现,不直接开放给客户。 |

BIOS子系统 |

单板BIOS软件系统,主要负责根据License决定对加速器哪些模块初始化,并上报加速器 |

BMC子系统 |

服务器BMC软件系统,在这里主要负责对加速器License的管理。 |

父主题: 鲲鹏加速引擎 开发指南(KAEzip)