CACHELINE对齐优化

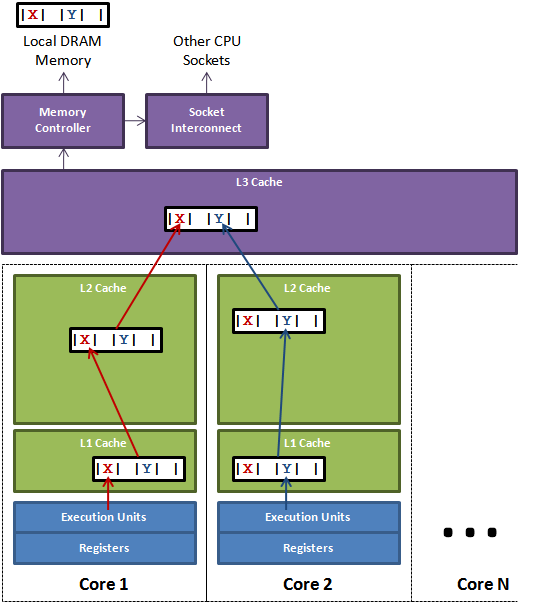

多并发编程中的临界区变量属于写频率高的变量,如锁中的lockword,会由于上锁和释放锁等操作不停地修改状态,每次修改都会导致其他core中的CACHELINE失效。避免此类数据结构与其他变量间的干扰,会在应用中对该CACHELINE做对齐操作,使得该变量独占一个CACHELINE。

|

Cacheline/Byte |

x86 |

鲲鹏920 |

|---|---|---|

|

L1 |

64 |

64 |

|

L2 |

64 |

64 |

|

L3 |

64 |

128 |

MySQL中对x86平台做了很多CACHELINE的64字节对齐,由于鲲鹏920处理器的L3 CACHELINE为128字节,因此需要将MySQL源码中的对齐方式修改为128字节。修改的对齐数据结构如下:

brt_search_latches btr_search_sys

ReadView::m_view_list

trx_sys_t::rw_trx_list

trx_sys_t::mysql_trx_list

trx_sys_t::rsegs

srv_conc_t::n_active

srv_conc_t::n_active

lock_sys_t::mutex

lock_sys_t::wait_mutex

MySQL中原64Byte对齐的数据结构修改为128Byte对齐。

修改后,TPM提升至3%~4%。

父主题: MySQL