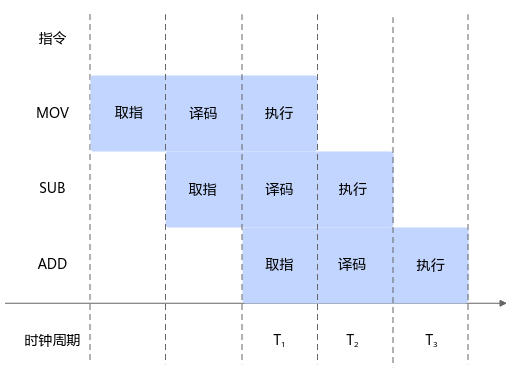

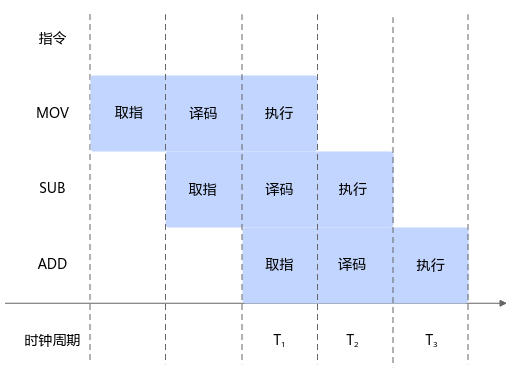

简单的三级流水线

先来了解下比较简单的三级指令流水线结构,包括取指、译码、执行三个部分,其中取指和译码可以在一个周期内处理完成,但是执行单元完成了大量的工作,包括与操作数相关的寄存器和存储器的读写操作、ALU操作及相关器件之间的数据传输,这就导致执行单元可能需要占用多个时钟周期,阻塞流水线上其他指令执行,成为了系统的性能瓶颈。

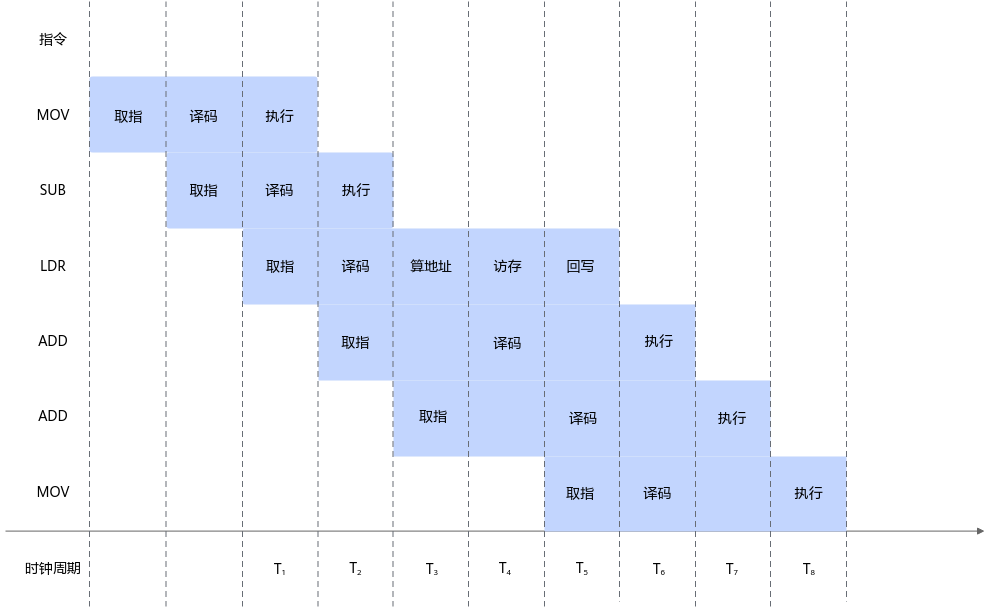

图1 理想的三级流水线

从T1时刻开始,每个Cycle均可以执行一条指令即IPC=1。这是理想的指令执行方式,流水线的执行效率是最高的。但是并不是所有的指令都是单周期指令。比如对存储器的访问指令LDR就是非单周期指令,这种指令会中断流水线的执行,如图2所示。

LDR指令是从内存中加载数据到寄存器中,这个指令的执行操作占用了T3~T5三个周期。T3时刻,计算存储器的地址,需要占用控制信号线,而译码的过程同样需要占用控制信号线。所以T3时刻第一条ADD的译码动作不能被执行,第二条ADD的取指操作不受影响;T4时刻,LDR指令正在访问内存,释放了控制信号线,所以第一条ADD的译码操作被执行,第二条ADD的译码操作本周期不能被执行。由于采用的是冯·诺伊曼体系结构,数据和指令共用存储器,访问内存的时候不能进行指令的读取操作。因此MOV指令的取指操作被中断。T5时刻,从内存中取出来数据放到CPU的寄存器中,这个操作需要占用执行单元,第一条ADD指令被中断,第二条ADD指令此时进入译码器进行译码操作,MOV指令的取指操作也被执行。

上面T3~T5三个周期,只执行了一条指令。整体上看,T1~T8,8个周期执行了6条指令,即IPC=0.75。分析上面指令执行过程,可以很清晰地看到是LDR这个多周期指令,在“执行”阶段占用了三个时钟周期,导致后面的指令执行受阻,流水线的执行效率降低。

父主题: 流水线